### CALIFORNIA STATE UNIVERSITY, NORTHRIDGE

## OPERATING CHARACTERISTICS OF UTILITY INTERACTIVE INVERTERS USED IN PHOTOVOLTAIC SYSTEMS

A graduate project submitted in partial fulfillment of the requirements For the degree of Master of Science in Electrical Engineering

By

Gevork Mkrtchyan

May 2012

The graduate project of Gevork Mkrtchyan is approved:

Professor Benjamin F. Mallard

Dr. Xiyi Hang

Professor Bruno Osorno, Chair

California State University, Northridge

Date

Date

Date

### DEDICATION

This graduate project is dedicated to my family, both immediate and extended. Without their support my accomplishments would mean nothing. To all of the professors at California State University, Northridge who provided their knowledge, wisdom and expertise not only in their respective fields but also in regards to life. To my wife Nikki, to whom I owe my life to; without her unending support throughout these past couple of years, I would not be writing this sentence. Finally, to my son, whom I expect to see very soon, may you aspire to and achieve all the dreams that fill your mind.

## TABLE OF CONTENTS

| Signature Page                                           | ii   |

|----------------------------------------------------------|------|

| Dedication                                               | iii  |

| List of Tables                                           | vii  |

| List of Figures                                          | viii |

| Abstract                                                 | xvi  |

| Introduction                                             | 1    |

| Photovoltaic Theory                                      | 4    |

| Introduction                                             | 4    |

| Semiconductors                                           | 7    |

| A Complete Photovoltaic System                           | 13   |

| Power Electronics Theory – As It Relates to the Inverter | 18   |

| Introduction                                             | 18   |

| Steady State Concepts and Fourier Analysis               | 19   |

| Semiconductor Switches                                   | 24   |

| The Basic Inverter                                       | 31   |

| Inverter Control Schemes – Single Phase                  | 34   |

| Inverter Control Schemes – Three Phase                   | 40   |

| Inverter Topologies                                      | 45   |

| Standards for the Utility Interactive Photovoltaic Inverter                                       | 48 |

|---------------------------------------------------------------------------------------------------|----|

| Design Considerations in Accordance with IEEE 1547 –<br>Interconnection of Distributed Generation | 48 |

| Utility Synchronization                                                                           | 52 |

| Introduction                                                                                      | 52 |

| The Fourier Adaptive Filter                                                                       | 52 |

| The Discrete Fourier Adaptive Filter                                                              | 54 |

| The Basic Phase-Locked Loop                                                                       | 57 |

| In-Quadrature Phase Detection                                                                     | 62 |

| T/4 Transport Delay PLL                                                                           | 65 |

| Adaptive Filtering PLL – Enhanced PLL                                                             | 66 |

| Second-Order Adaptive Filtering PLL                                                               | 68 |

| Second-Order Generalized Integrator PLL                                                           | 71 |

| SOGI Frequency-Locked Loop                                                                        | 73 |

| Anti-Islanding Considerations                                                                     | 77 |

| Introduction                                                                                      | 77 |

| The Non-Detection Zone                                                                            | 77 |

| Utility Detection of Islanding                                                                    | 79 |

| Passive Detection of Islanding                                                                    | 79 |

| Active Detection of Islanding                                                                     | 80 |

| Maximum Power Point Tracking                  | 85  |

|-----------------------------------------------|-----|

| Introduction                                  | 85  |

| Perturb and Observe                           | 85  |

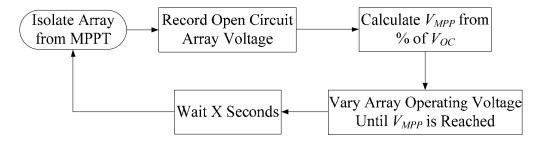

| Constant Voltage                              | 87  |

| Pilot Cell                                    | 87  |

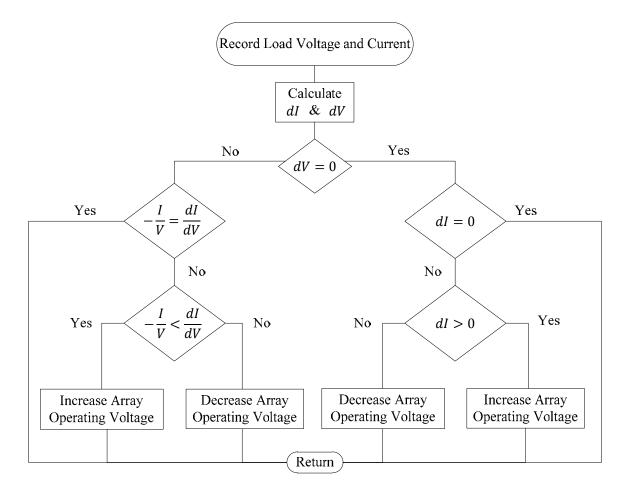

| Incremental Conductance                       | 88  |

| Model Based Algorithms                        | 89  |

| Computer Simulations                          | 90  |

| Photovoltaic Array                            | 90  |

| MPPT Implementation and Buck Converter Design | 98  |

| Full Bridge Inverter                          | 116 |

| PWM Control                                   | 117 |

| SOGI-FLL with Gain Optimization               | 120 |

| Complete Circuit                              | 128 |

| Conclusion                                    | 140 |

| References                                    | 141 |

## LIST OF TABLES

| 1. | Specifications of a typical 156mm x 156mm monocrystalline silicon cell at STC (1 Kw/m <sup>2</sup> , 25°C, AM 1.5) | 15 |

|----|--------------------------------------------------------------------------------------------------------------------|----|

| 2. | Specifications of a typical 50 cell photovoltaic module at STC (1 Kw/m <sup>2</sup> , 25°C, AM 1.5) [7]            | 16 |

| 3. | Ratings of a 10-module series array using modules with specifications shown in Table 2                             | 16 |

| 4. | IEEE 1547 Disconnection Requirements for Voltage Deviation                                                         | 48 |

| 5. | IEEE 1547 Disconnection Requirement for Frequency Deviation                                                        | 49 |

| 6. | IEEE 1547 Maximum Allowable Current Harmonics                                                                      | 49 |

| 7. | Calculated model parameters of a commercial grade photovoltaic cell                                                | 91 |

## LIST OF FIGURES

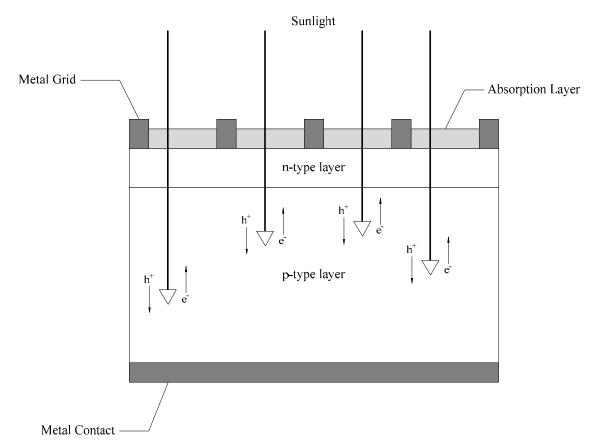

| 1.  | A conventional solar cell. Creation of electron-hole pairs, e <sup>-</sup> and h <sup>+</sup> .<br>Generated current flows between the metal grid and metal contact,<br>which are opposite in polarity due to the migration of<br>electrons and holes                                                                                                       | 5  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

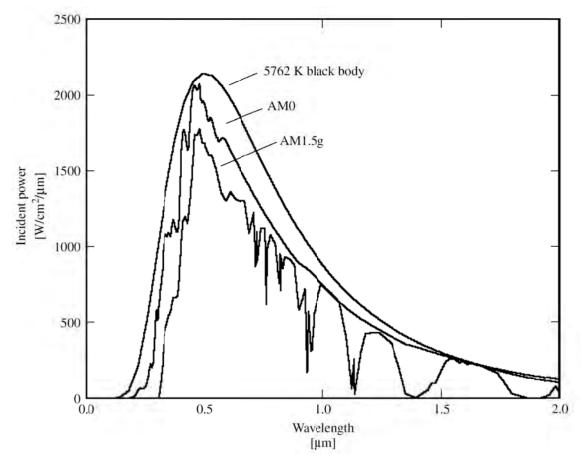

| 2.  | The radiation spectrum for a black-body at 5762 K, an AM0 spectrum, and an AM1.5 global spectrum [2]                                                                                                                                                                                                                                                        | 6  |

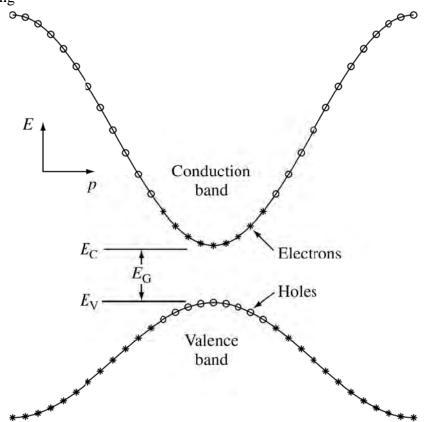

| 3.  | A simplified energy band diagram at $T > 0$ K for a direct<br>band gap ( $E_G$ ) semiconductor [2]                                                                                                                                                                                                                                                          | 8  |

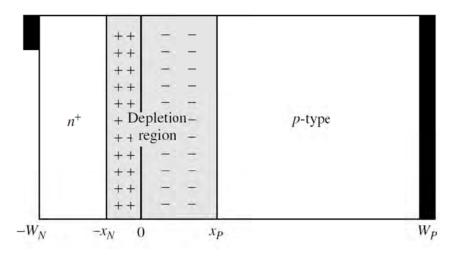

| 4.  | Simple solar cell structure used to analyze the operation of a solar cell. Free carriers have diffused across the junction $(x = 0)$ leaving a space-charge or depletion region practically devoid of any free or mobile charges. The fixed charges in the depletion region are due to ionized donors on the n-side and ionized acceptors on the p-side [2] | 9  |

| 5.  | A simple solar cell circuit model. Diode 1 represents recombination<br>in the quasi-neutral region, while diode 2 represents the<br>recombination in the depletion region                                                                                                                                                                                   | 10 |

| 6.  | Current-voltage characteristic of a typical silicon solar cell [2]                                                                                                                                                                                                                                                                                          | 11 |

| 7.  | Solar Cell Connection a) Series Connection of Solar Cells<br>b) Parallel Connection of Solar Cells                                                                                                                                                                                                                                                          | 15 |

| 8.  | Electrical representation of a photovoltaic module with 50 series connected solar cells                                                                                                                                                                                                                                                                     | 16 |

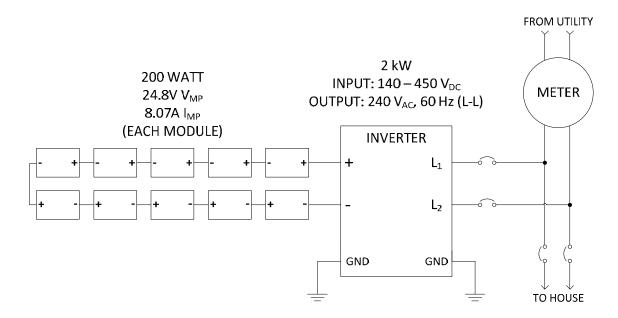

| 9.  | A simple 2 Kw photovoltaic system for a typical 4 person household                                                                                                                                                                                                                                                                                          | 17 |

| 10. | Block Diagram of an elementary power electronic system                                                                                                                                                                                                                                                                                                      | 18 |

| 11. | Example of a waveform with transient and steady state responses                                                                                                                                                                                                                                                                                             | 19 |

| 12. | Example of a nonsinusoidal waveform with multiple frequency Components                                                                                                                                                                                                                                                                                      | 22 |

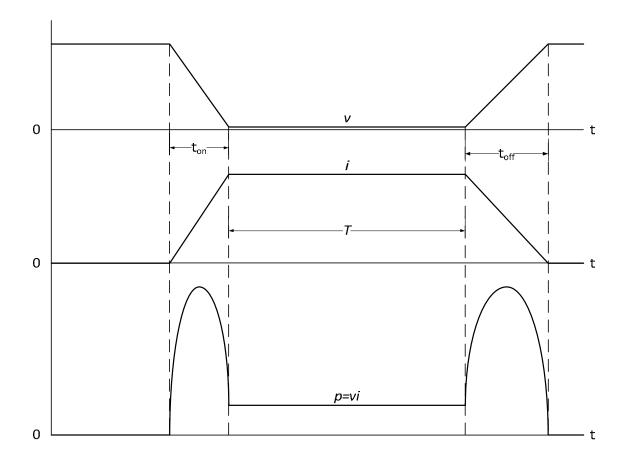

| 13. | Voltage, Current and Power Loss waveforms of a semiconductor switch                                                         | 24 |

|-----|-----------------------------------------------------------------------------------------------------------------------------|----|

| 14. | The semiconductor structure and circuit symbol of a typical power diode                                                     | 25 |

| 15. | Voltage-Current characteristics of a typical power diode<br>(Different scales are used for positive and negative half-axes) | 26 |

| 16. | The semiconductor structure and circuit symbol of a typical power BJT                                                       | 27 |

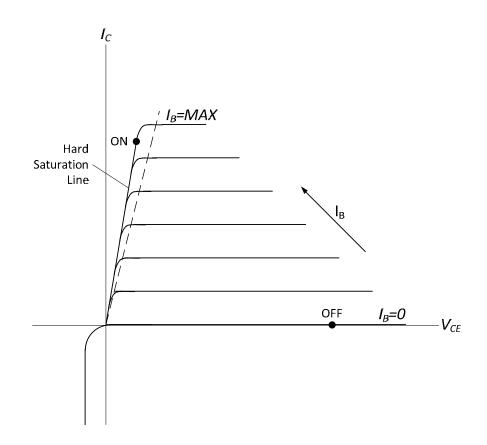

| 17. | Voltage-Current characteristics of a typical power BJT                                                                      | 28 |

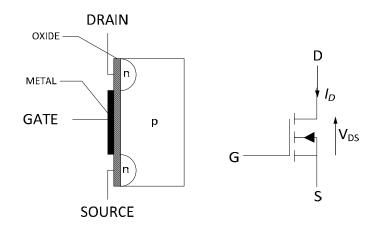

| 18. | The semiconductor structure and circuit symbol of a typical power MOSFET                                                    | 29 |

| 19. | Voltage-Current characteristics of a typical power MOSFET                                                                   | 29 |

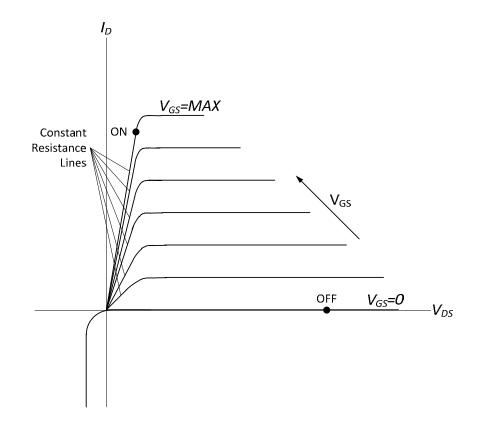

| 20. | The equivalent circuit and circuit symbol of a typical IGBT                                                                 | 30 |

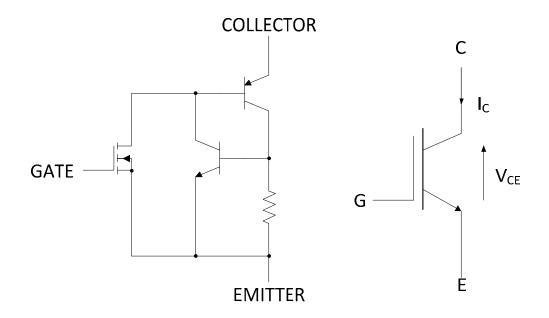

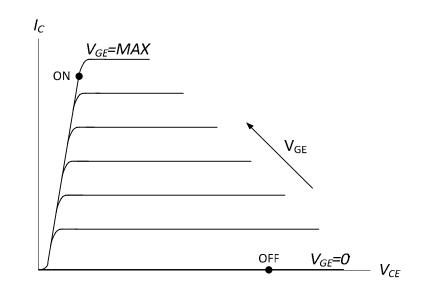

| 21. | Voltage-Current characteristics of a typical IGBT                                                                           | 31 |

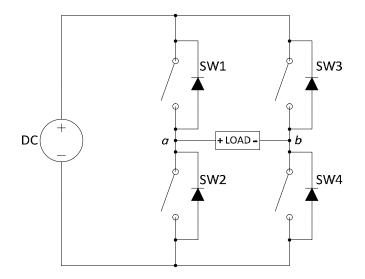

| 22. | Fundamental inverter circuit using McMurray's H-Bridge topology                                                             | 31 |

| 23. | H-Bridge inverter a) positive current at load, b) negative current flow at load                                             | 32 |

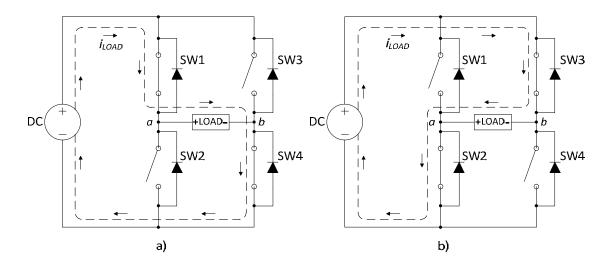

| 24. | Voltage and Current waveforms of circuit in Figure 23                                                                       | 33 |

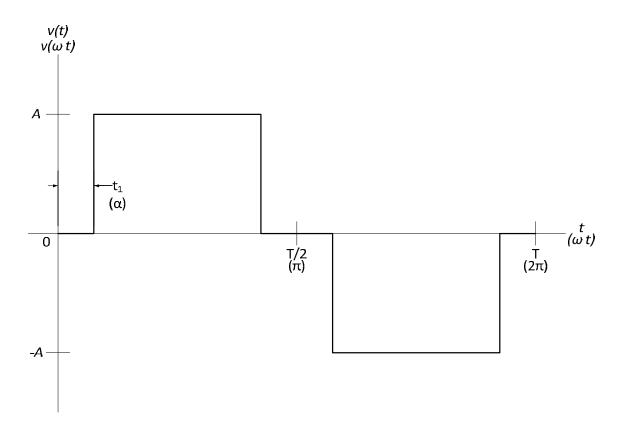

| 25. | General square wave function with duty cycle variable $t_1$                                                                 | 35 |

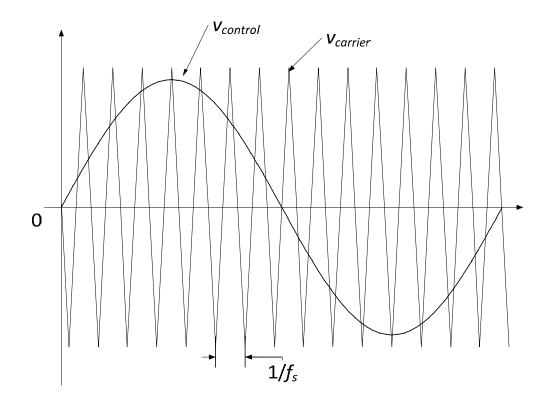

| 26. | PWM with bipolar voltage switching, showing control and carrier signals                                                     | 37 |

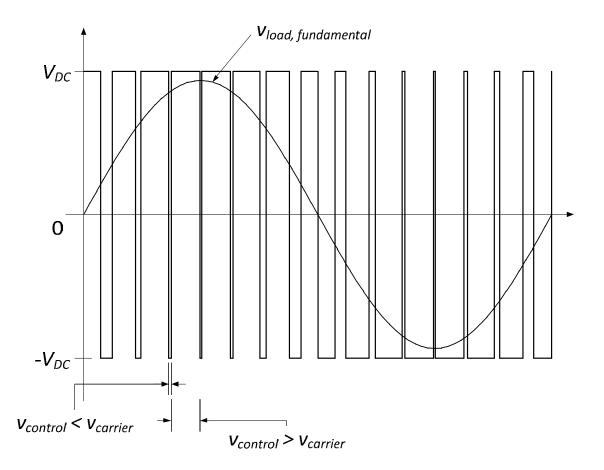

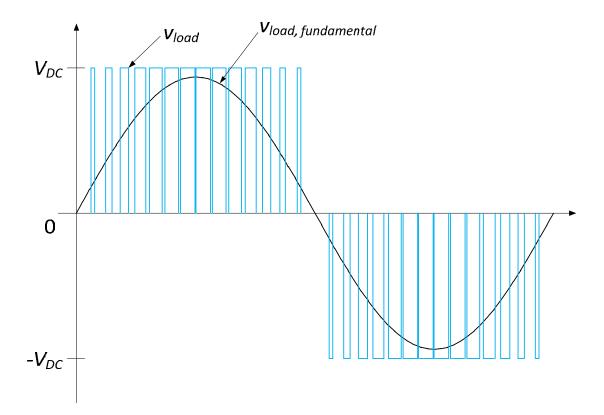

| 27. | Bipolar PWM voltage waveform at the load of circuit in Figure 22                                                            | 38 |

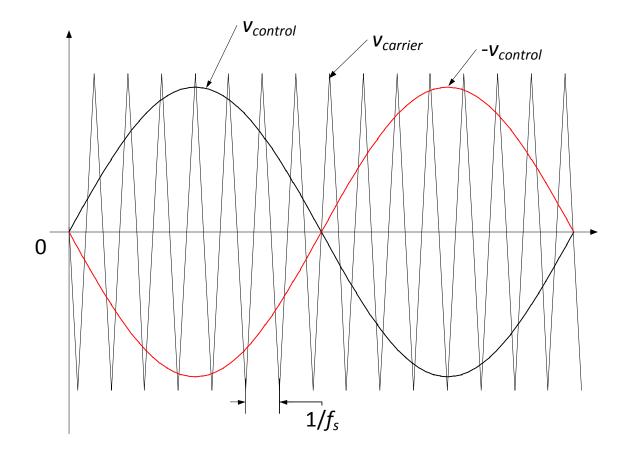

| 28. | PWM with unipolar switching, showing control and carrier signals                                                            | 39 |

| 29. | Unipolar PWM voltage waveform at the load of circuit in Figure 22                                                           | 41 |

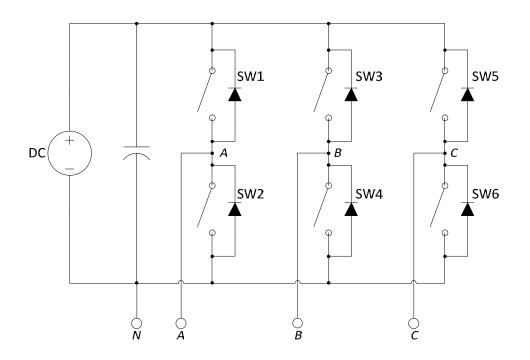

| 30. | General 3-phase inverter circuit                                                                                            | 41 |

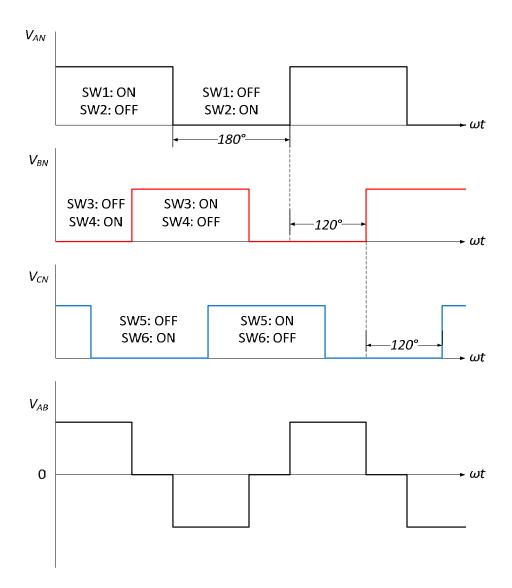

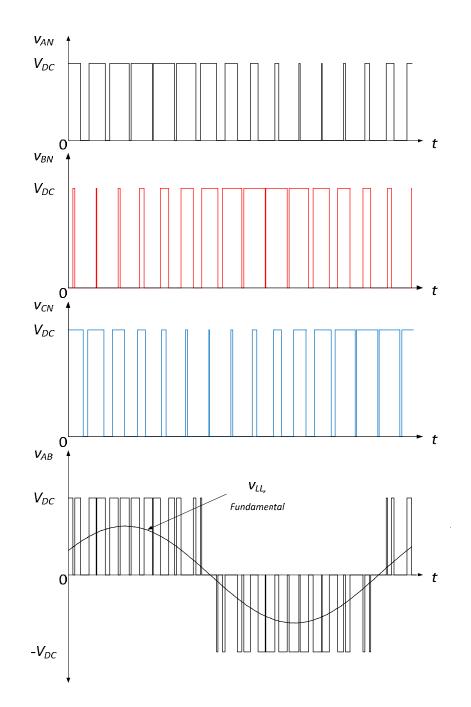

| 31. | Three-phase square wave inverter voltage waveforms ( $V_{BC}$ and $V_{CA}$ not shown) | 42 |

|-----|---------------------------------------------------------------------------------------|----|

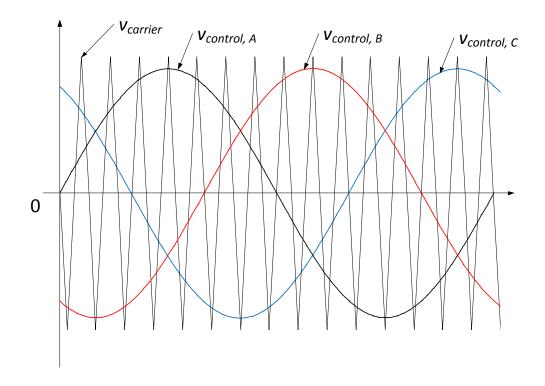

| 32. | Three-phase control and carrier waveforms for PWM                                     | 43 |

| 33. | Three-phase PWM inverter voltage waveforms ( $V_{BC}$ and $V_{CA}$ not shown)         | 44 |

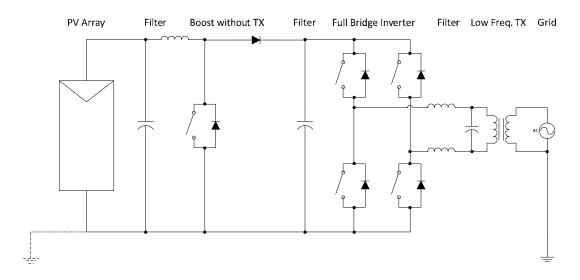

| 34. | Low frequency transformer topology                                                    | 46 |

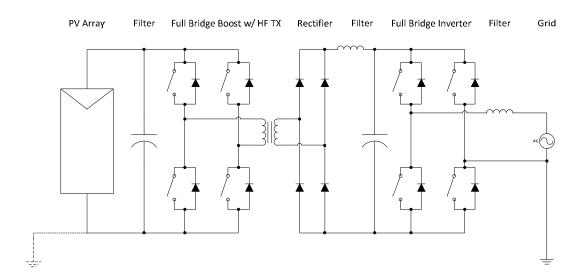

| 35. | High frequency transformer topology with boosting inverter                            | 46 |

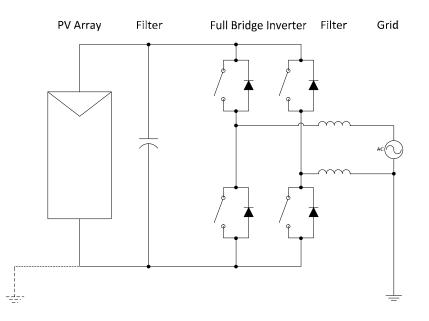

| 36. | Transformerless inverter topology                                                     | 47 |

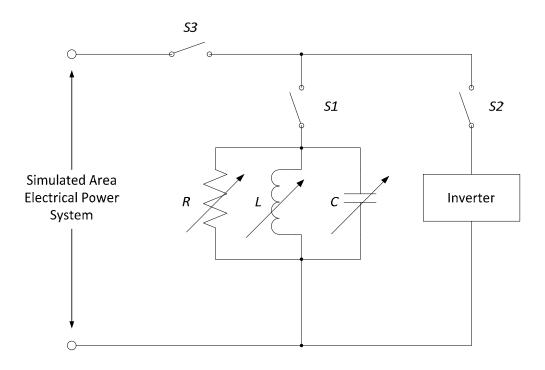

| 37. | IEEE 1547 Anti-islanding test setup                                                   | 50 |

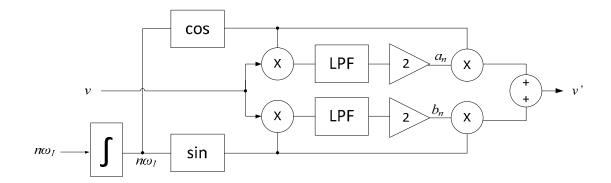

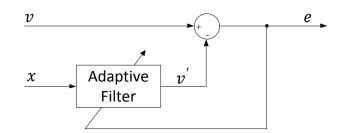

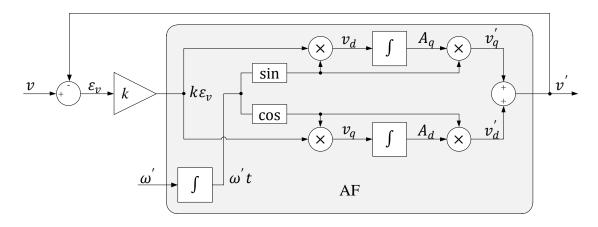

| 38. | Adaptive filter based on Fourier series decomposition                                 | 53 |

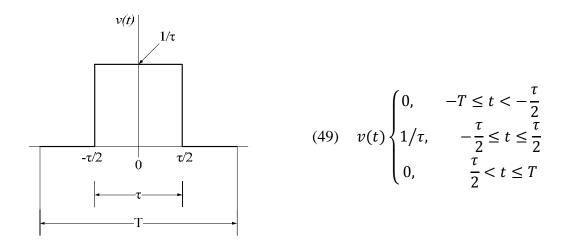

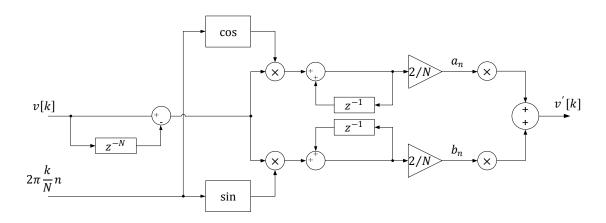

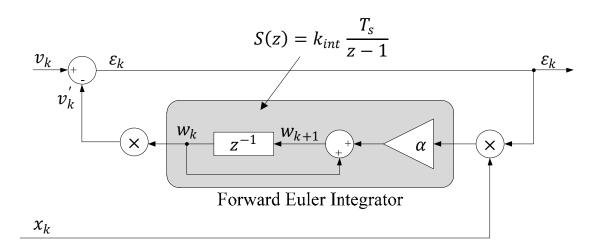

| 39. | Discrete adaptive filter based on the RDFT                                            | 57 |

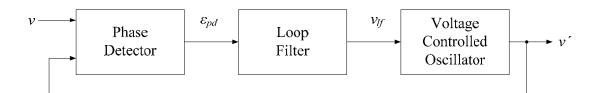

| 40. | Basic structure of a PLL                                                              | 57 |

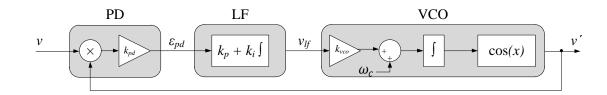

| 41. | Block diagram of an elementary PLL                                                    | 58 |

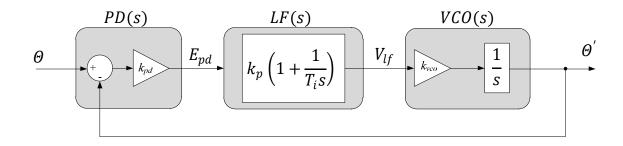

| 42. | Small signal model of an elementary PLL                                               | 60 |

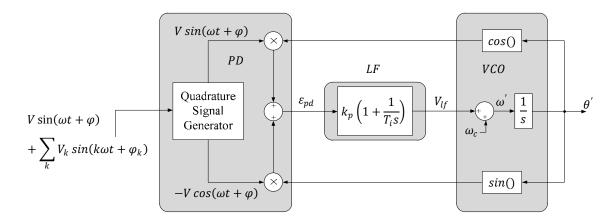

| 43. | Diagram of a PLL with an in-quadrature PD                                             | 62 |

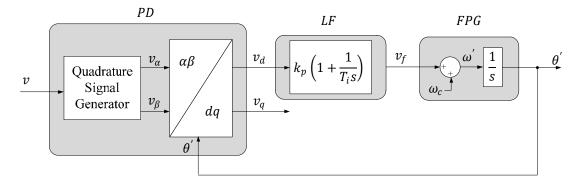

| 44. | PD based on the quadrature signal generator and the Park transformation               | 63 |

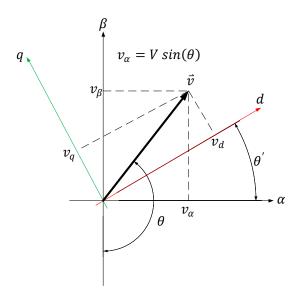

| 45. | Vector representation of the QSG output signals                                       | 64 |

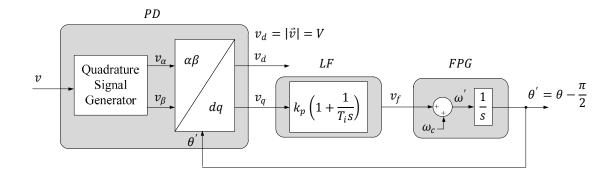

| 46. | PLL with the LF on the <i>q</i> axis of the QSG                                       | 65 |

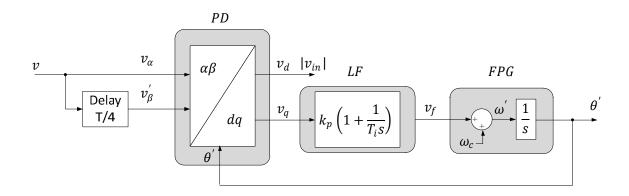

| 47. | PLL based on a T/4 transport delay                                                    | 65 |

| 48. | Adaptive noise cancelling (ANC) system                                                | 66 |

| 49. | A simple least mean square algorithm with one weight                                  | 67 |

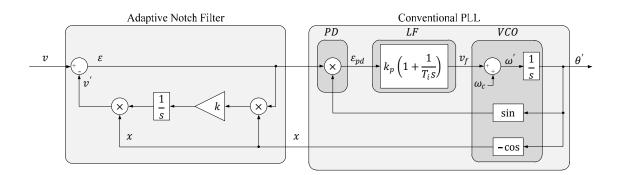

| 50. | Enhanced PLL (EPLL)                                                                       | 68 |

|-----|-------------------------------------------------------------------------------------------|----|

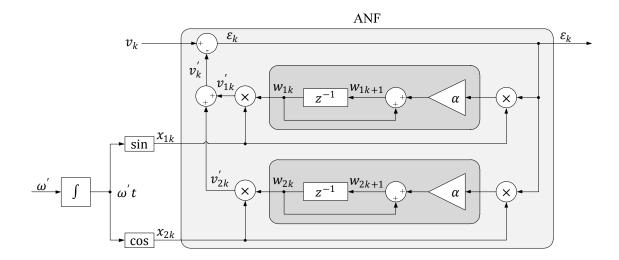

| 51. | Discrete form of second order ANF with LMS algorithm                                      | 69 |

| 52. | Second order adaptive filter in the continuous time domain                                | 69 |

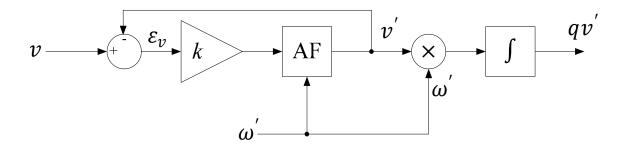

| 53. | QSG based on a second order AF                                                            | 71 |

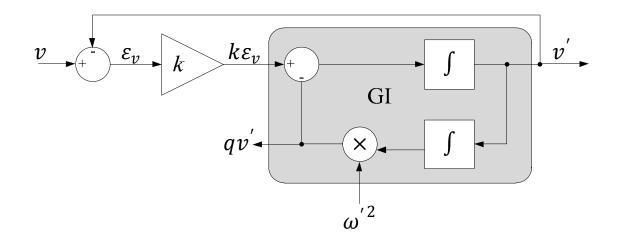

| 54. | Second order AF based on general integrator (GI)                                          | 72 |

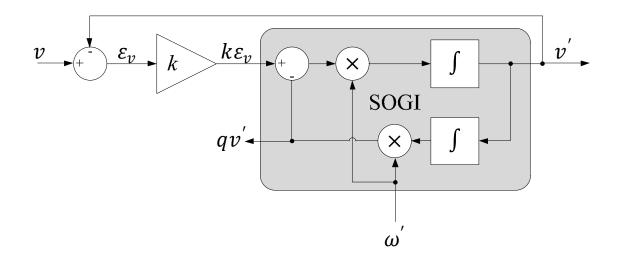

| 55. | Second order adaptive filter based on a Second Order<br>Generalized Integrator (SOGI-QSG) | 72 |

| 56. | SOGI-based PLL (SOGI-PLL)                                                                 | 73 |

| 57. | Bode plot of $E(s)$ and $Q(s)$                                                            | 74 |

| 58. | SOGI-based QSG with FLL                                                                   | 75 |

| 59. | SOGI-FLL with FLL gain normalization                                                      | 76 |

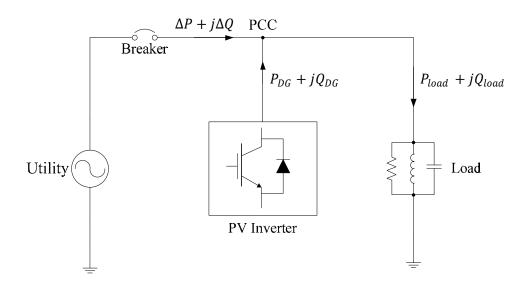

| 60. | Diagram of test set-up required by IEEE 1547                                              | 78 |

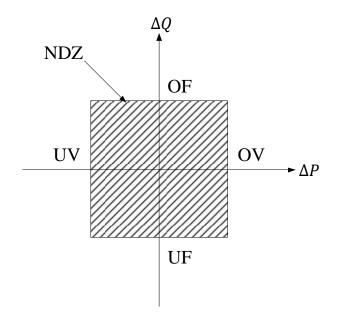

| 61. | The non-detection zone (NDZ)                                                              | 78 |

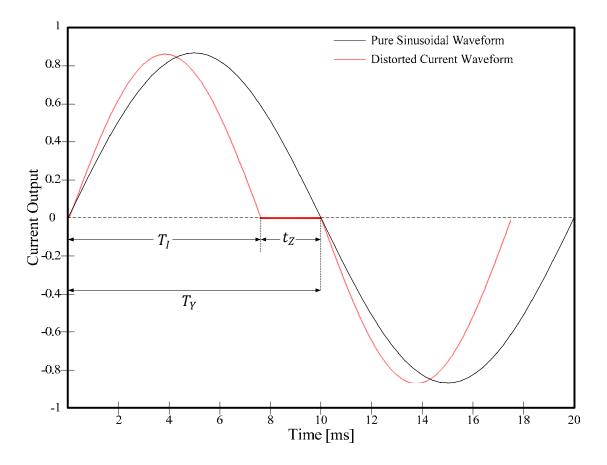

| 62. | Current waveform using the AFD method                                                     | 81 |

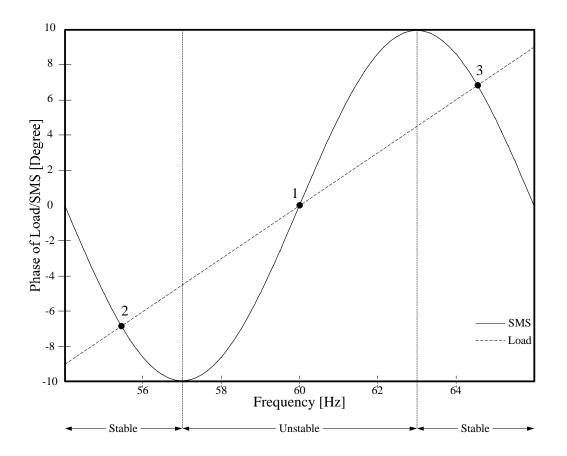

| 63. | Phase vs Frequency relationship in the SMS method                                         | 82 |

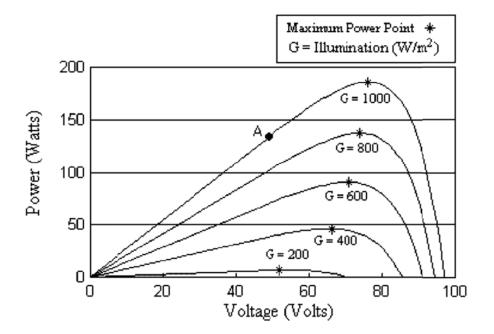

| 64. | Photovoltaic array power-voltage relationship [18]                                        | 86 |

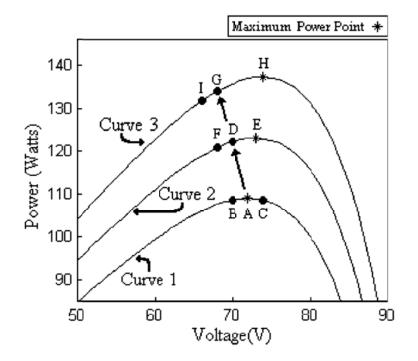

| 65. | Erratic behavior of P&O under rapidly increasing irradiance [18]                          | 86 |

| 66. | Perturb & Observe (P&O) MPPT algorithm                                                    | 87 |

| 67. | Incremental Conductance (IC) MPPT algorithm                                               | 89 |

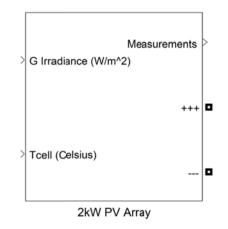

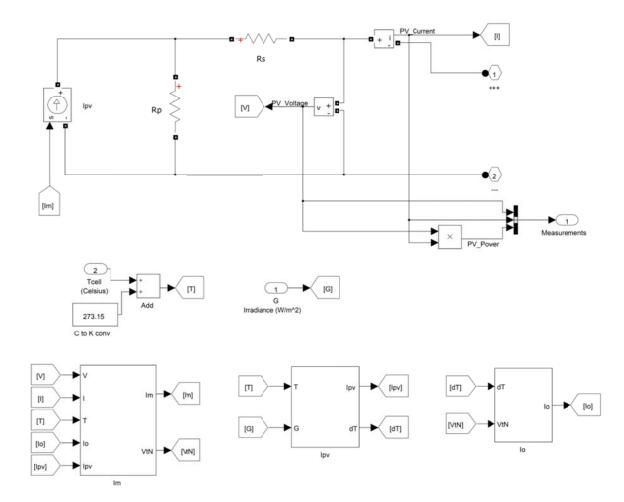

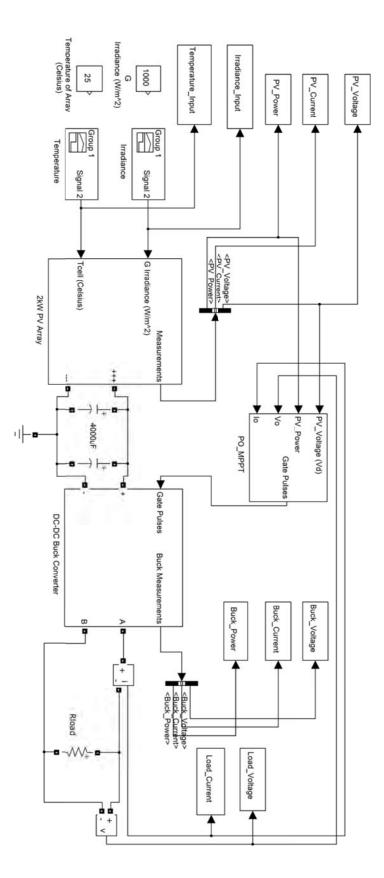

| 68. | 2kW Photovoltaic Array control block                                                      | 92 |

| 69. | 2kW Photovoltaic Array equivalent circuit and model                                                        | 92  |

|-----|------------------------------------------------------------------------------------------------------------|-----|

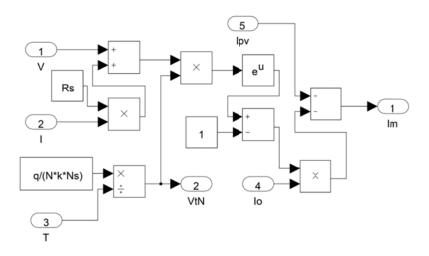

| 70. | $I_m$ block equivalent model                                                                               | 93  |

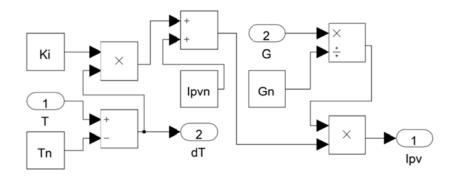

| 71. | $I_{pv}$ block equivalent model                                                                            | 93  |

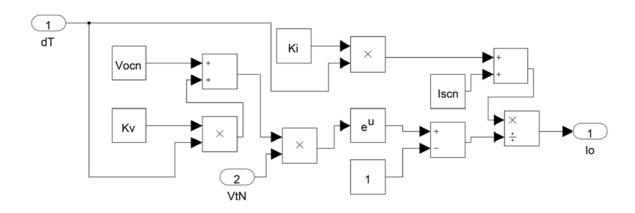

| 72. | <i>I</i> <sub>o</sub> block equivalent model                                                               | 93  |

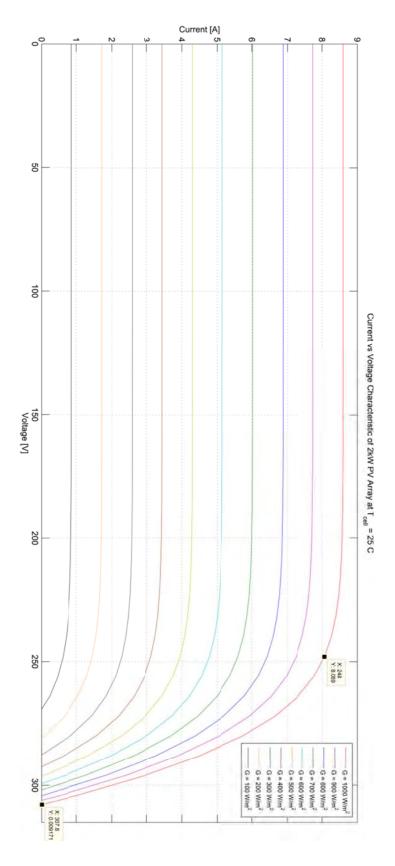

| 73. | Current vs Voltage characteristic plot of 2kW PV array at varying $G$ and $T_{cell} = 25 ^{\circ}\text{C}$ | 94  |

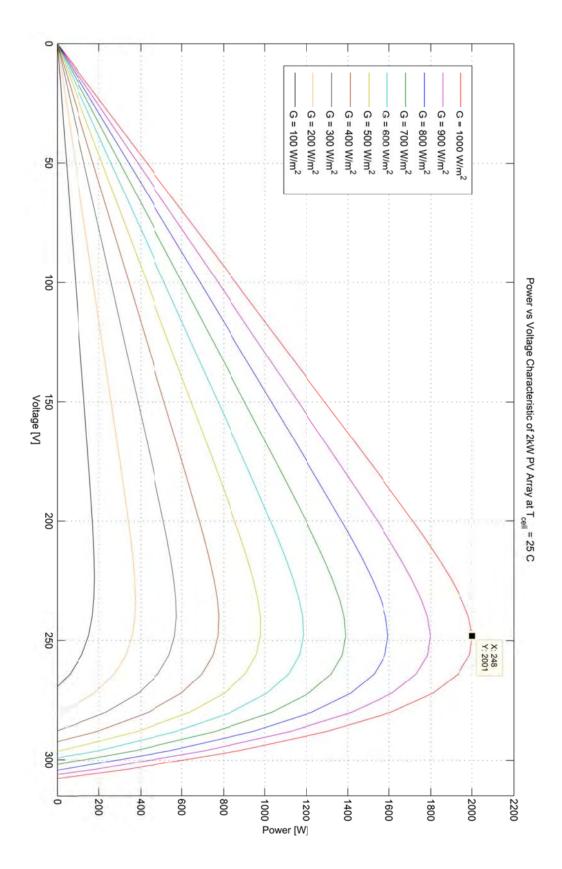

| 74. | Power vs Voltage characteristic plot of 2kW PV array at varying $G$ and $T_{cell} = 25 ^{\circ}\text{C}$   | 95  |

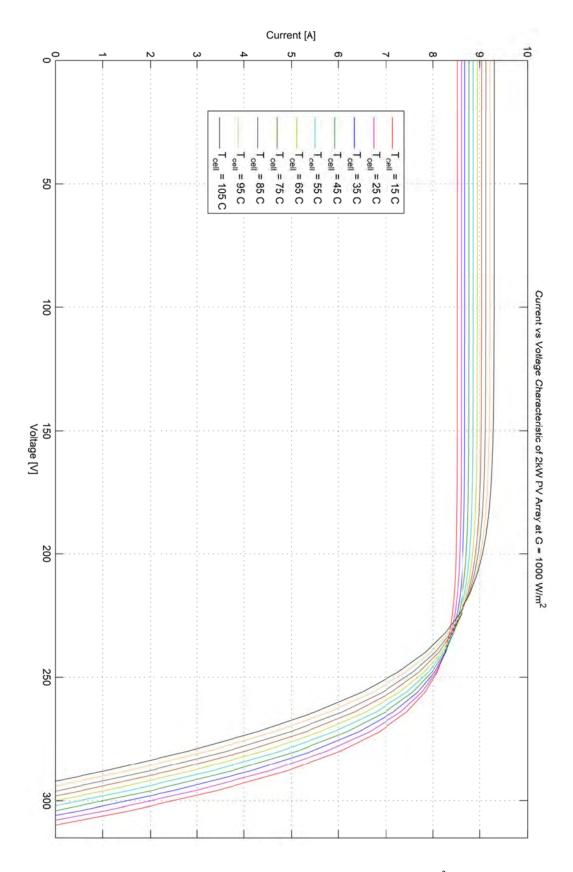

| 75. | Current vs Voltage characteristic plot of 2kW PV array at $G = 1$ kW/M <sup>2</sup> and varying $T_{cell}$ | 96  |

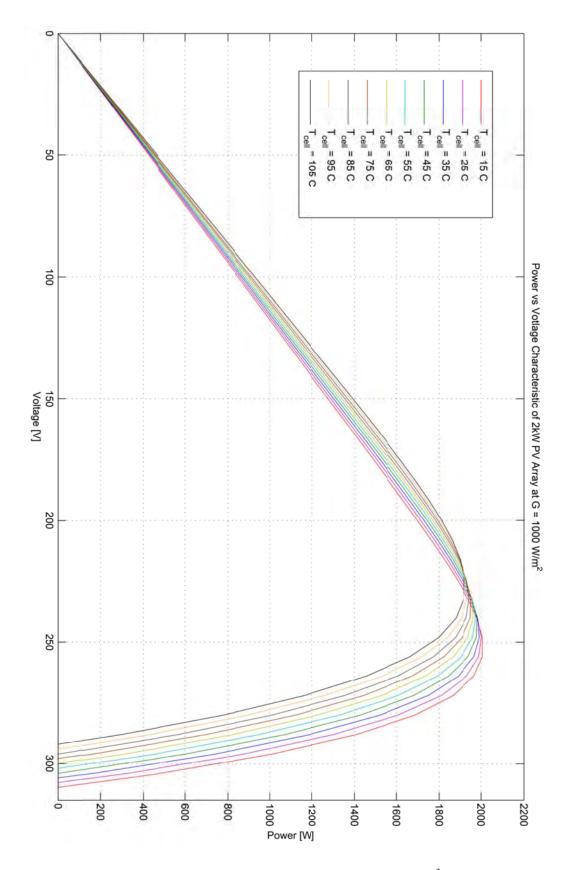

| 76. | Power vs Voltage characteristic plot of 2kW PV array at $G = 1$ kW/M <sup>2</sup> and varying $T_{cell}$   | 97  |

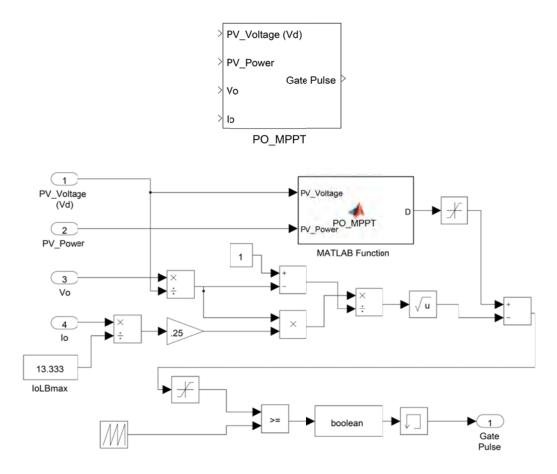

| 77. | MPPT Control block and equivalent circuit                                                                  | 99  |

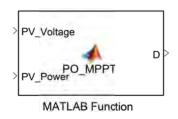

| 78. | MATLAB <sup>®</sup> script control block                                                                   | 99  |

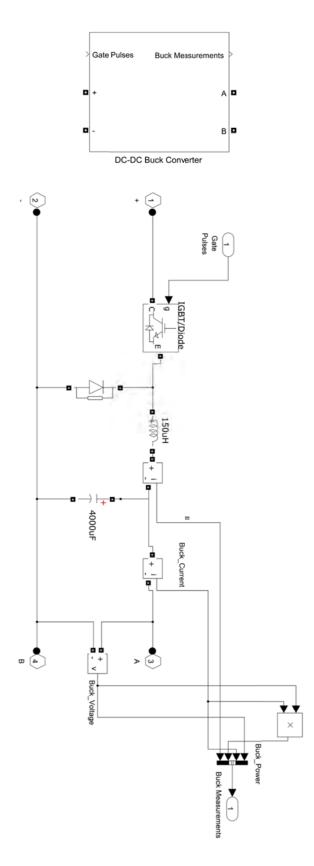

| 79. | Buck converter control block and equivalent circuit                                                        | 102 |

| 80. | PV Array and Buck converter simulation set-up                                                              | 103 |

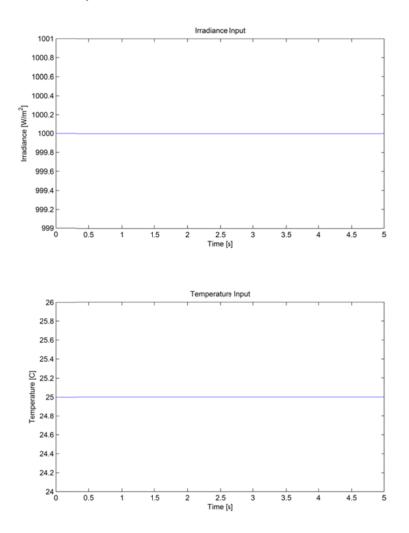

| 81. | Irradiance and Temperature Input waveforms for constant G, constant $T_{cell}$ simulation                  | 104 |

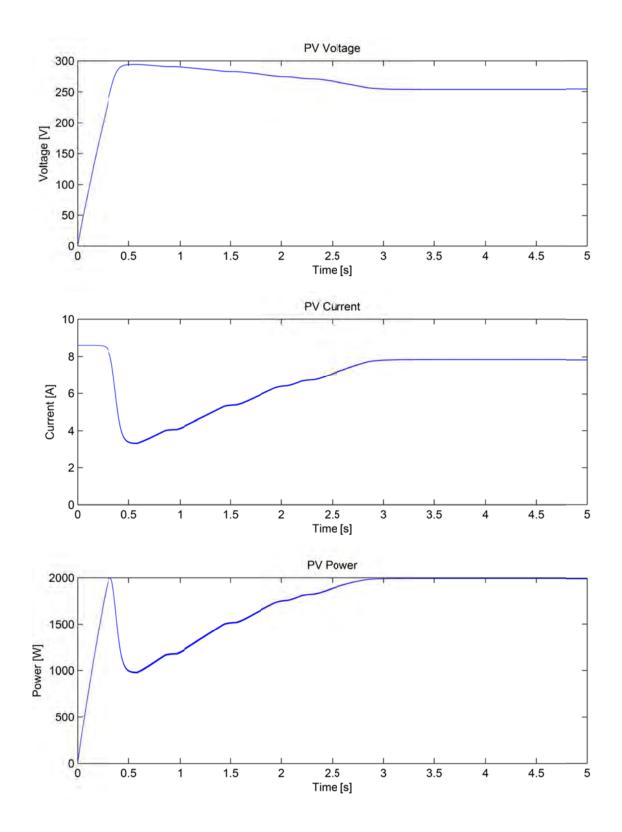

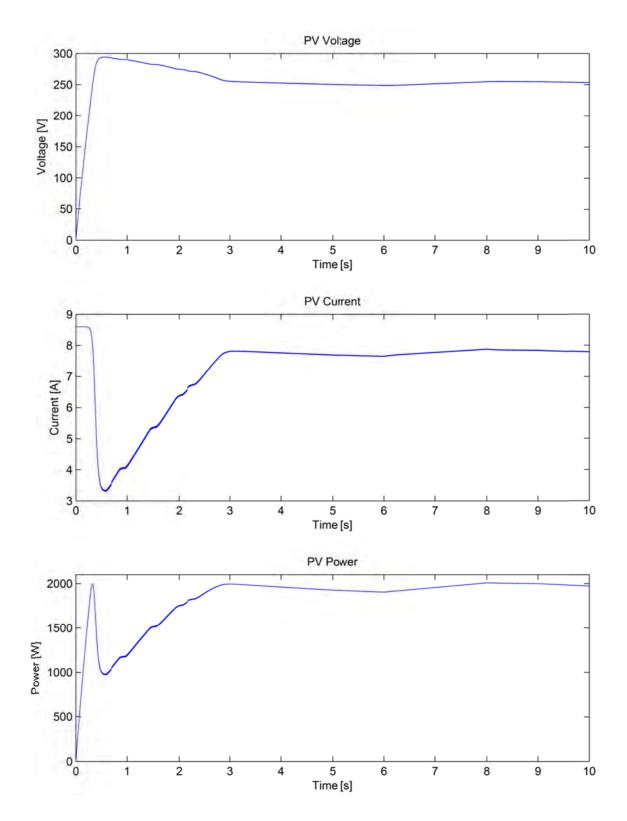

| 82. | PV output waveforms for constant G, constant $T_{cell}$ simulation                                         | 105 |

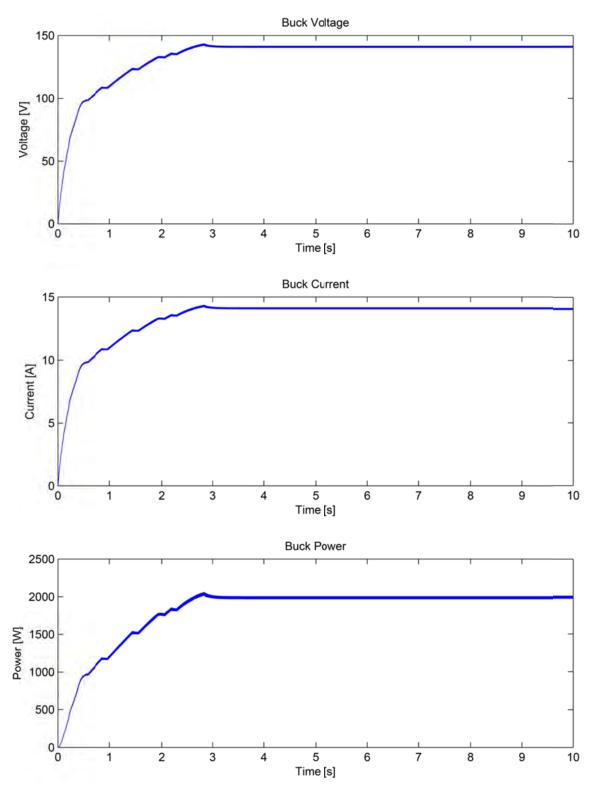

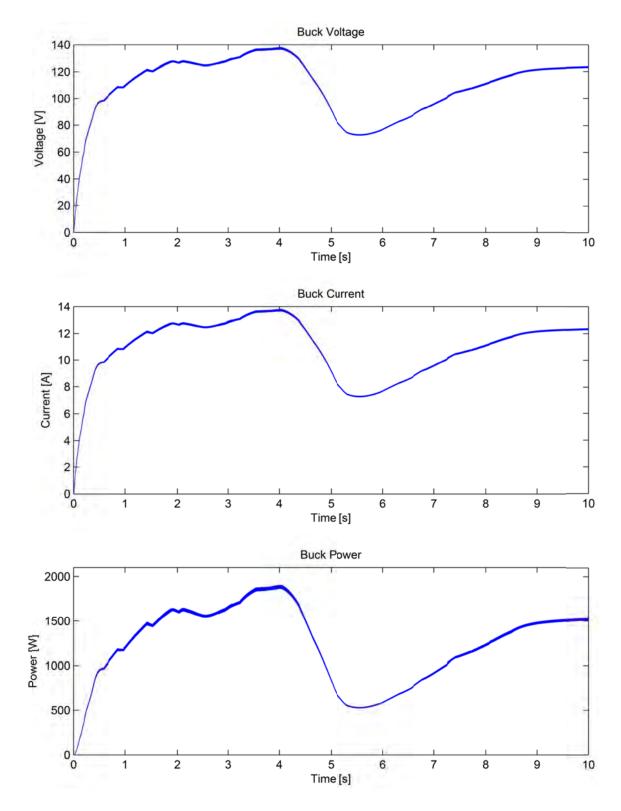

| 83. | Buck converter output waveforms for constant G, constant $T_{cell}$ simulation                             | 106 |

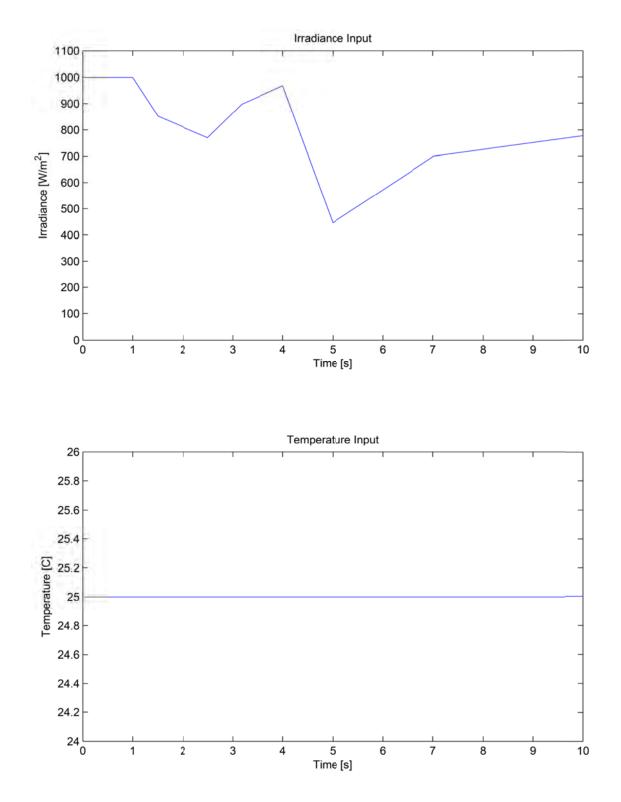

| 84. | Irradiance and Temperature Input waveforms for varying $G$ , constant $T_{cell}$ simulation                | 107 |

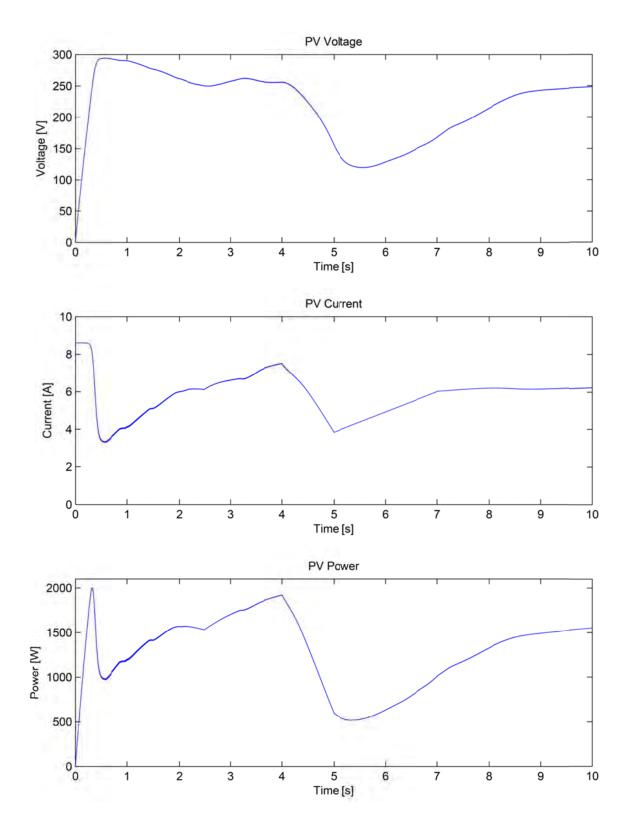

| 85.  | PV output waveforms for varying G, constant T <sub>cell</sub> simulation                    | 108 |

|------|---------------------------------------------------------------------------------------------|-----|

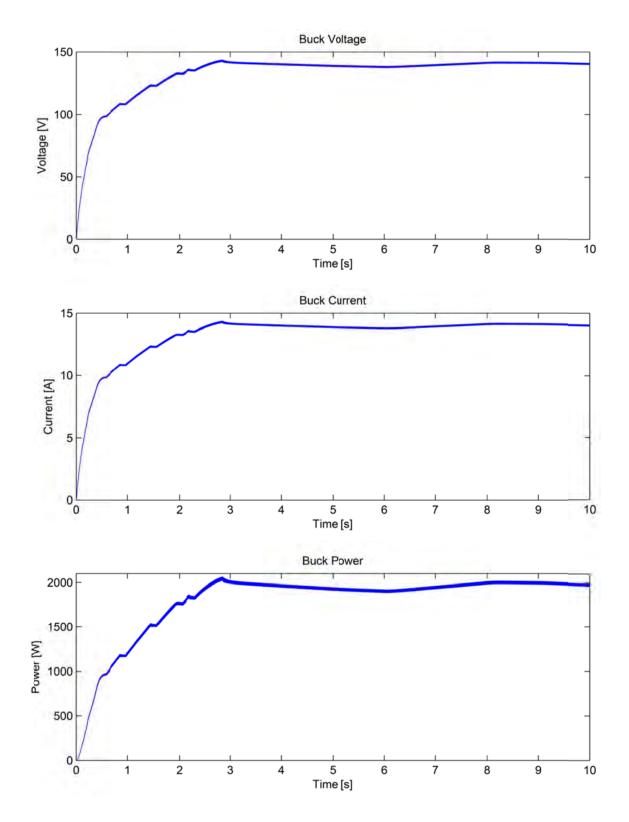

| 86.  | Buck converter output waveforms for varying G, constant $T_{cell}$ simulation               | 109 |

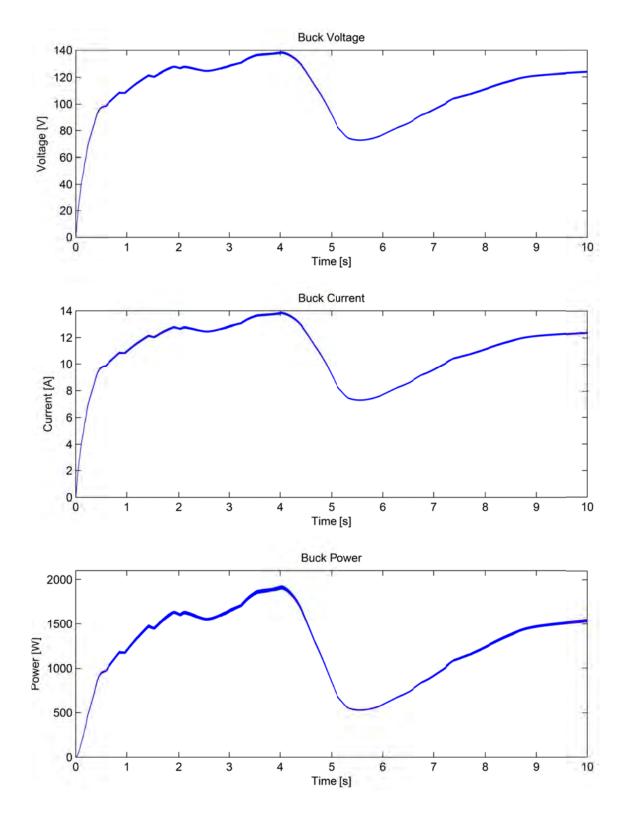

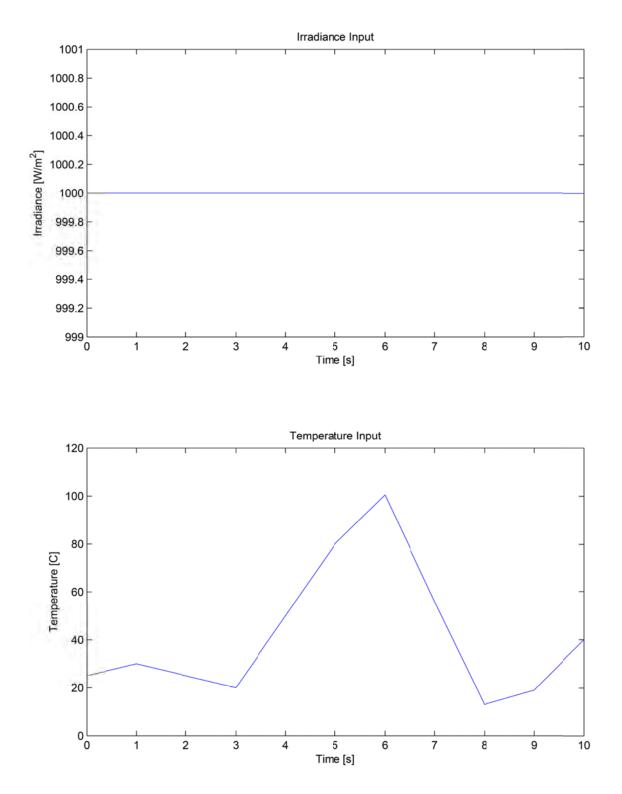

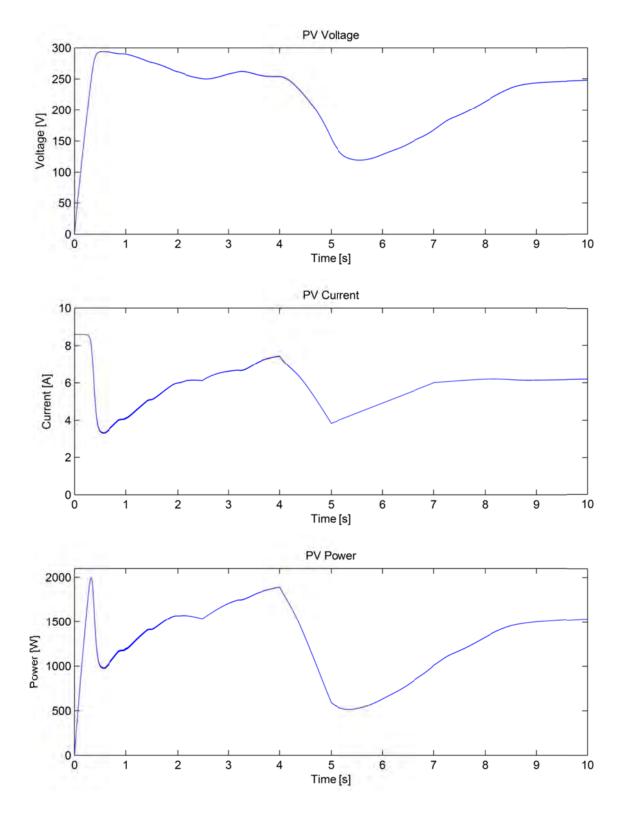

| 87.  | Irradiance and Temperature Input waveforms for constant $G$ , varying $T_{cell}$ simulation | 110 |

| 88.  | PV output waveforms for constant G, varying $T_{cell}$ simulation                           | 111 |

| 89.  | Buck converter output waveforms for constant G, varying $T_{cell}$ simulation               | 112 |

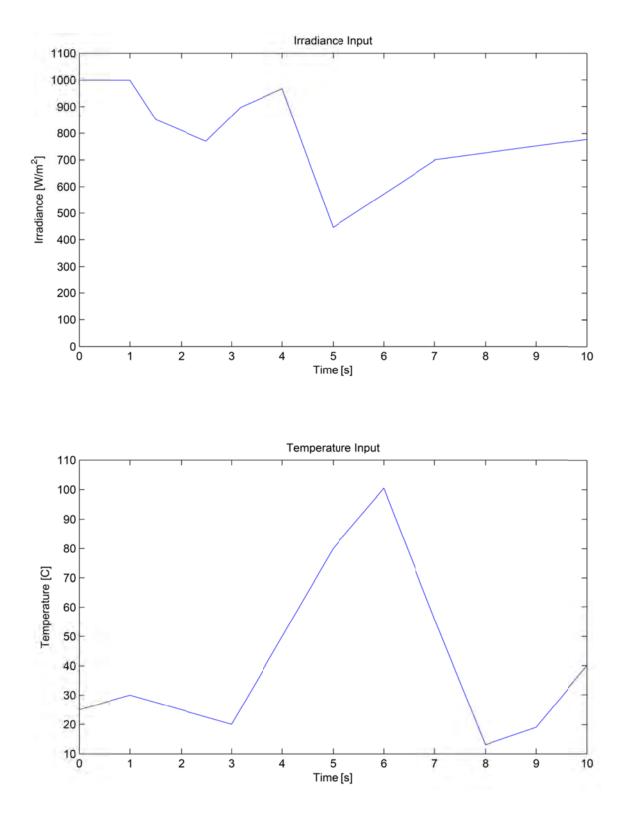

| 90.  | Irradiance and Temperature Input waveforms for varying $G$ , varying $T_{cell}$ simulation  | 113 |

| 91.  | PV output waveforms for varying G, varying T <sub>cell</sub> simulation                     | 114 |

| 92.  | Buck converter output waveforms for constant G, varying $T_{cell}$ simulation               | 115 |

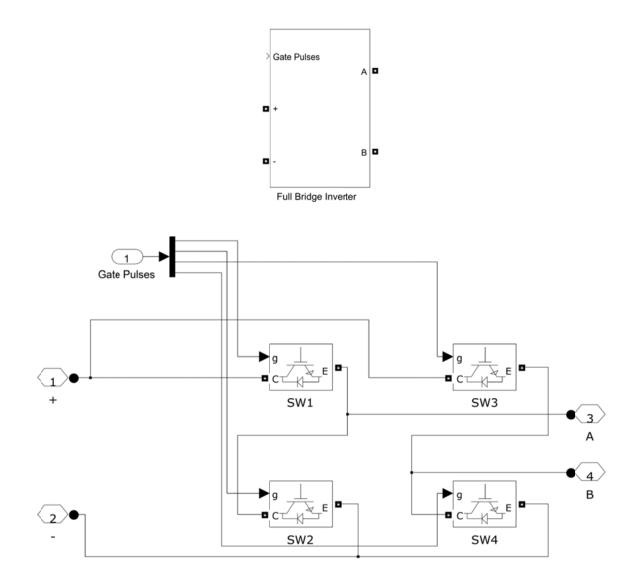

| 93.  | Full-bridge inverter control block and equivalent circuit                                   | 117 |

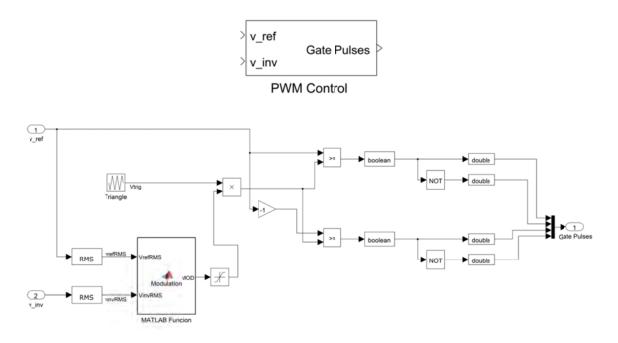

| 94.  | PWM control block employing unipolar switching logic                                        | 118 |

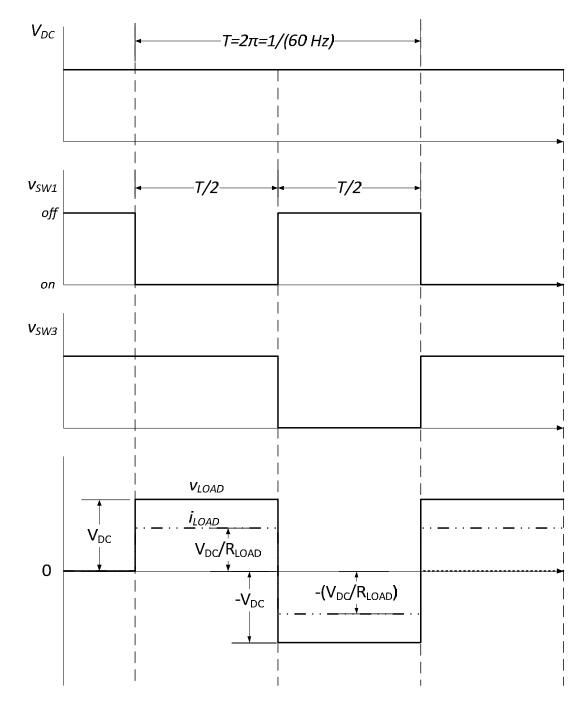

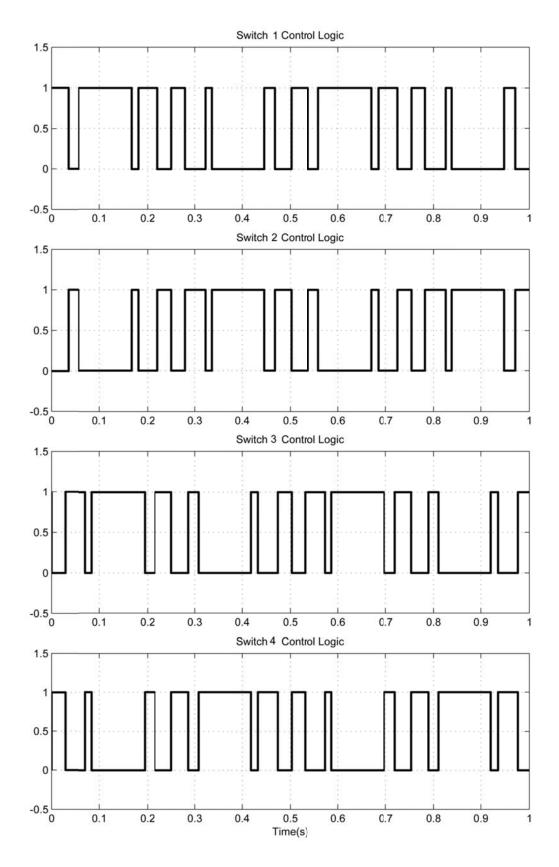

| 95.  | PWM control signals for switches SW1-SW4                                                    | 119 |

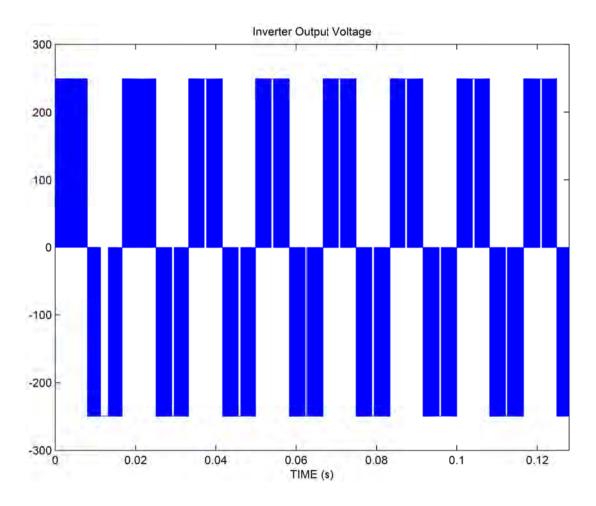

| 96.  | Inverter output voltage                                                                     | 120 |

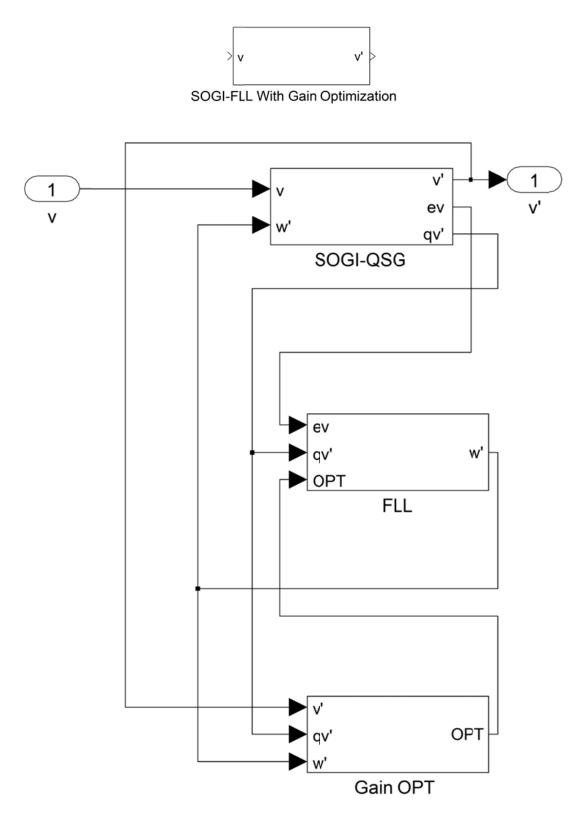

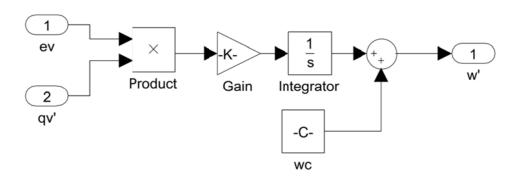

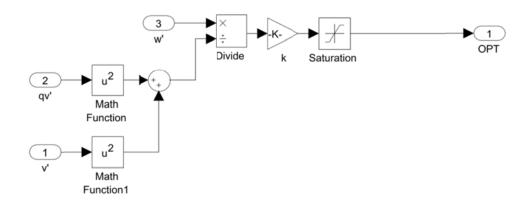

| 97.  | SOGI-FLL with Gain Optimization control block and equivalent circuit                        | 121 |

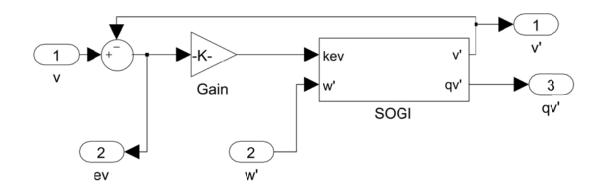

| 98.  | SOGI-QSG equivalent circuit                                                                 | 122 |

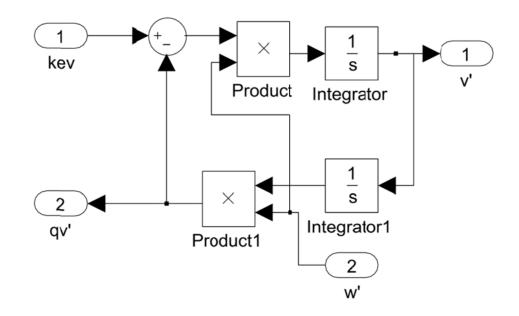

| 99.  | SOGI equivalent circuit                                                                     | 122 |

| 100. | FLL equivalent circuit                                                                      | 122 |

| 101. | Gain Optimization equivalent circuit                                                        | 123 |

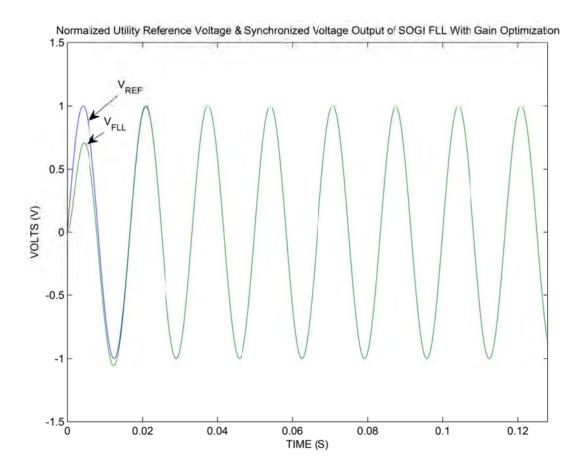

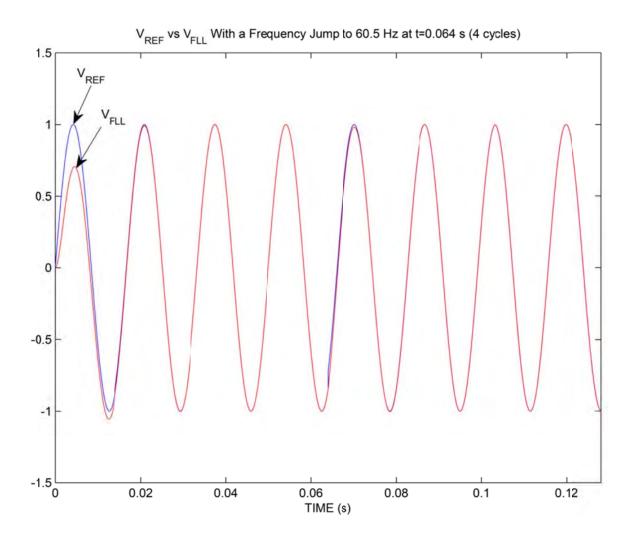

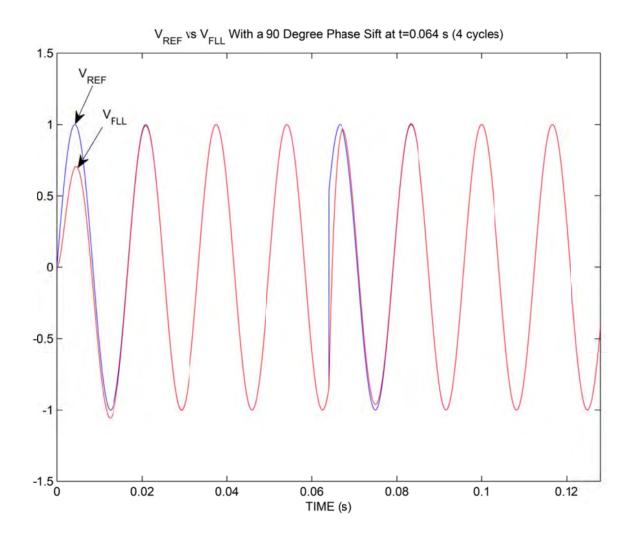

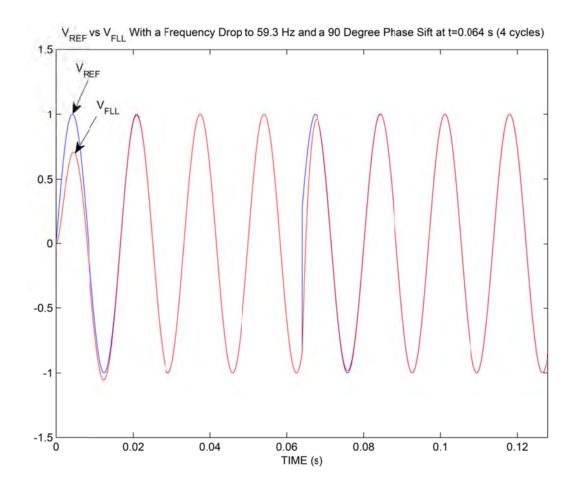

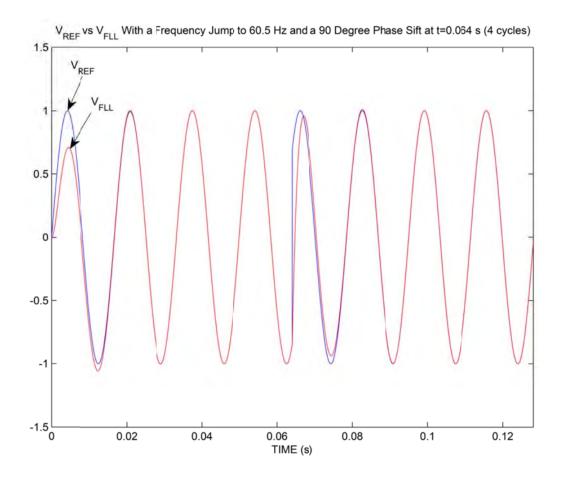

| 102. | Input and output waveforms of the SOGI-FLL                                                      | 123 |

|------|-------------------------------------------------------------------------------------------------|-----|

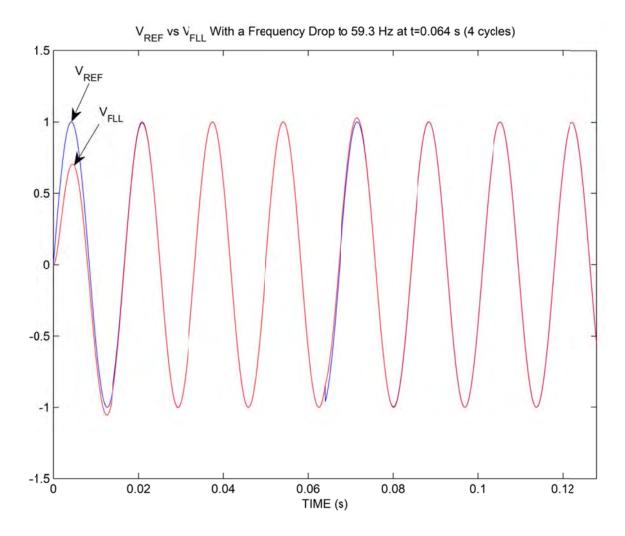

| 103. | Input and output waveforms of the SOGI-FLL experiencing a frequency drop                        | 124 |

| 104. | Input and output waveforms of the SOGI-FLL experiencing a frequency jump                        | 125 |

| 105. | Input and output waveforms of the SOGI-FLL experiencing a phase shift                           | 126 |

| 106. | Input and output waveforms of the SOGI-FLL experiencing a frequency drop and phase shift        | 127 |

| 107. | Input and output waveforms of the SOGI-FLL experiencing a frequency jump and phase shift        | 128 |

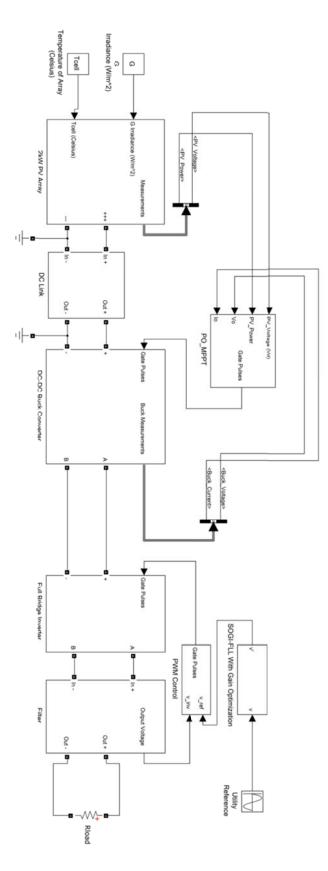

| 108. | Complete schematic of simulation test set-up for the utility interactive inverter               | 130 |

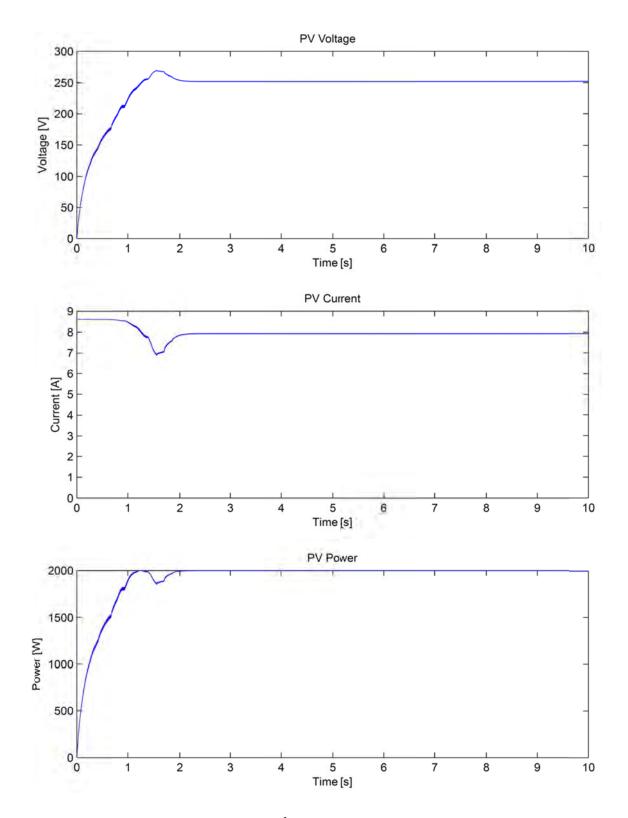

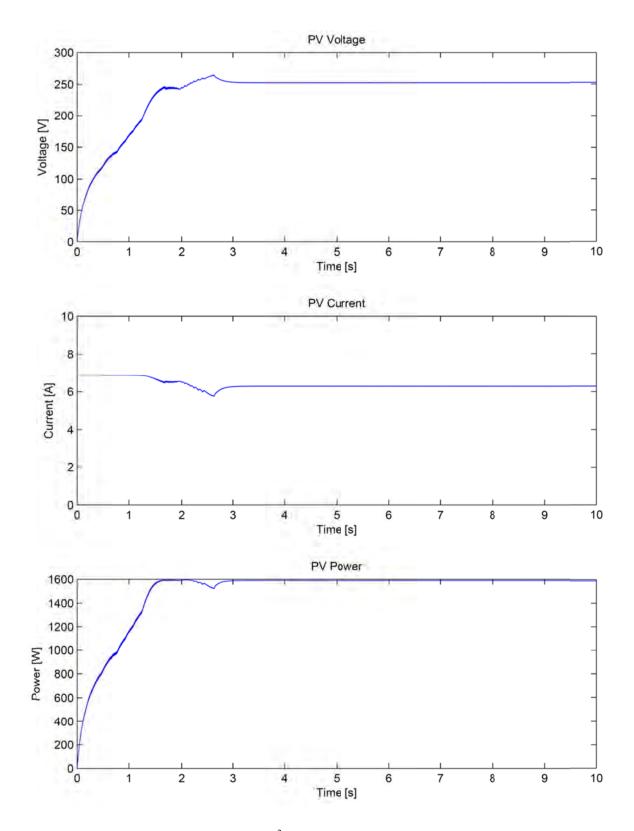

| 109. | PV array output at $G = 1000 \text{ W/m}^2$ of complete model simulation                        | 131 |

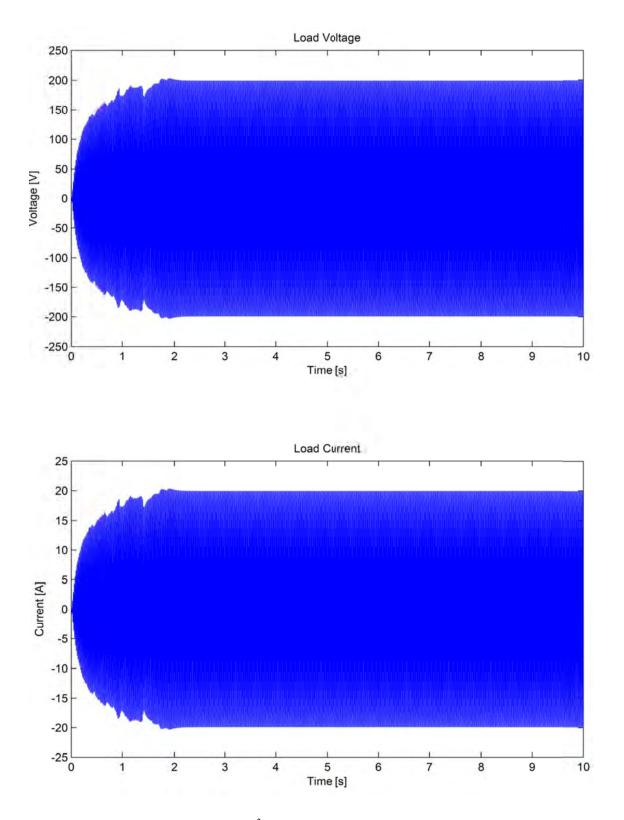

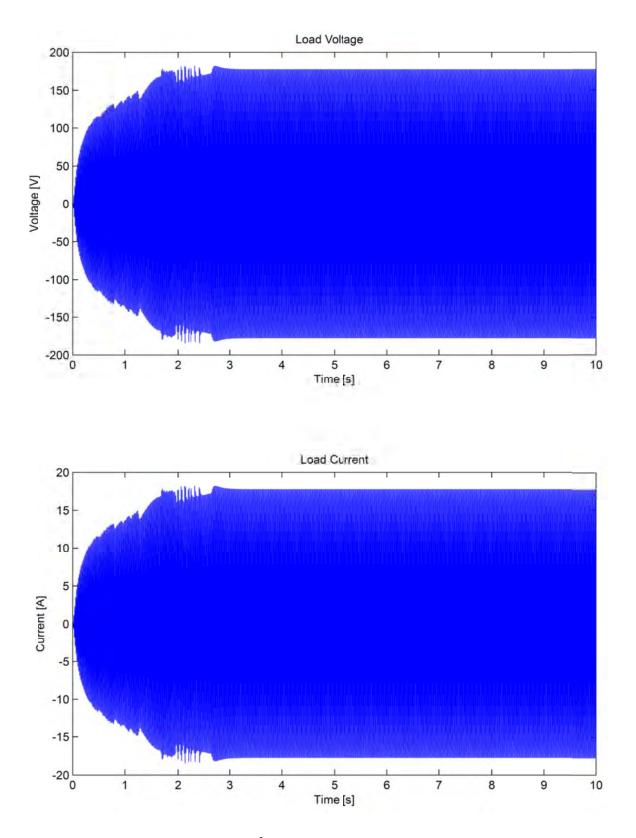

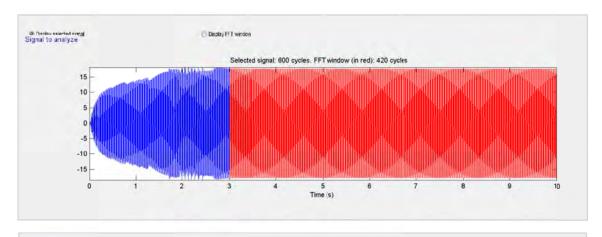

| 110. | Load output at $G = 1000 \text{ W/m}^2$ of complete model simulation                            | 132 |

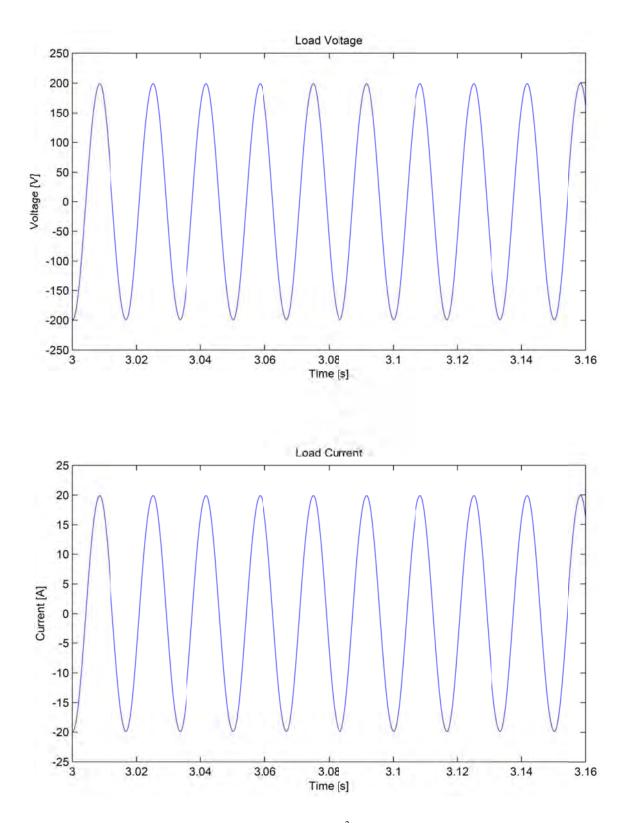

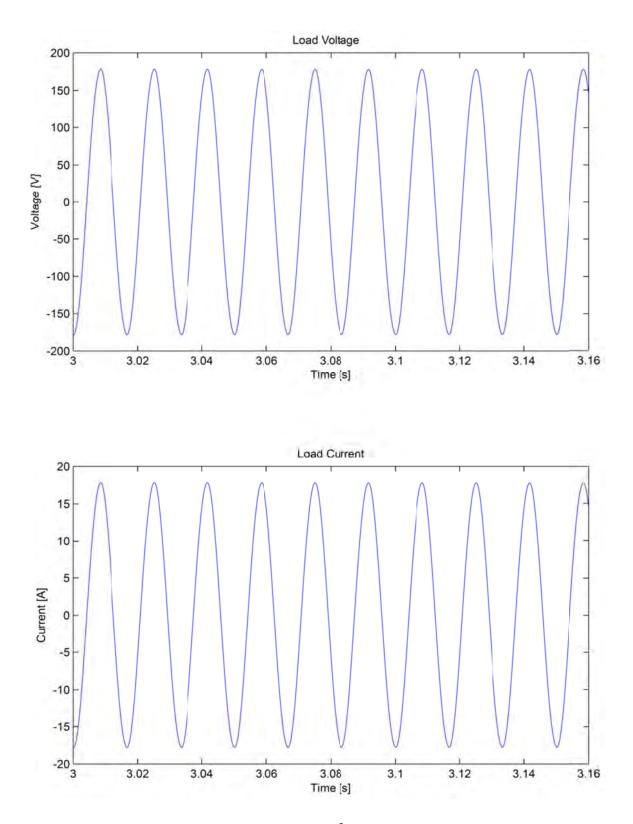

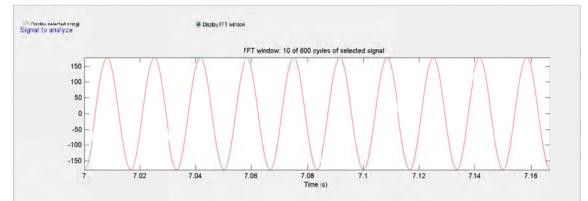

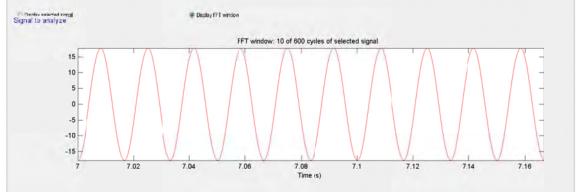

| 111. | 10 cycles of the load output at $G = 1000 \text{ W/m}^2$ of complete model simulation           | 133 |

| 112. | PV array output at $G = 800 \text{ W/m}^2$ of complete model simulation                         | 134 |

| 113. | Load output at $G = 800 \text{ W/m}^2$ of complete model simulation                             | 135 |

| 114. | 10 cycles of the load output at $G = 800 \text{ W/m}^2$ of complete model simulation            | 136 |

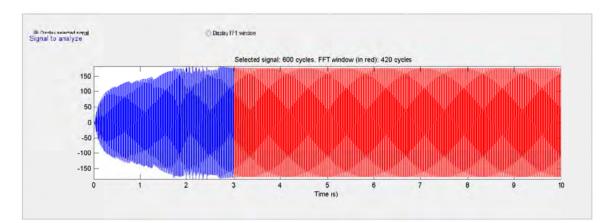

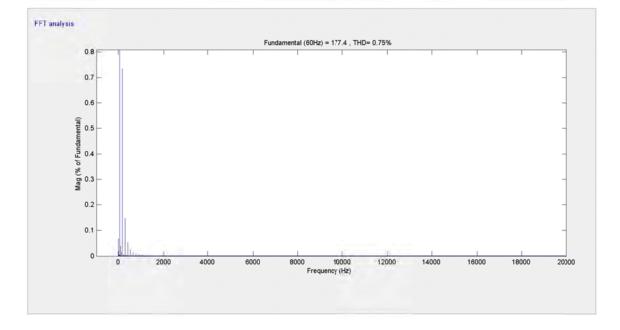

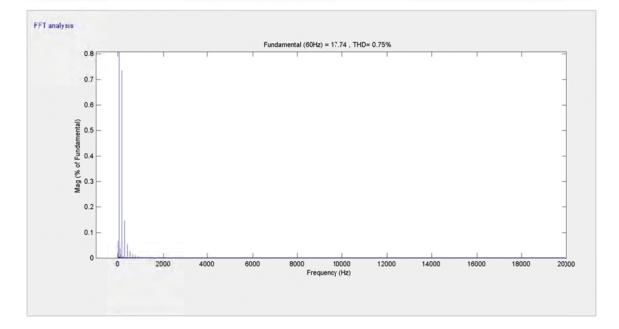

| 115. | MATLAB <sup>®</sup> FFT analysis tool output of the voltage waveform at $G = 800 \text{ W/m}^2$ | 137 |

## LIST OF FIGURES CONCLUDED

# 116. MATLAB<sup>®</sup> FFT analysis tool output of the current waveform at $G = 800 \text{ W/m}^2$

138

### ABSTRACT

### OPERATING CHARACTERISTICS OF UTILITY INTERACTIVE INVERTERS

### USED IN PHOTOVOLTAIC SYSTEMS

By

Gevork Mkrtchyan

Master of Science in Electrical Engineering

The fundamental operating characteristics of the utility interactive, or grid connected, inverter is explored. The foundation of photovoltaic and power electronics is established, along with the concept of waveform inversion leading to the understanding of the inner workings of the utility interactive inverter. Various topologies of the inverter design are presented, along with discussions regarding switching devices, of which it is determined that currently the IGBT semiconductor devices are more applicable. The concept of utility synchronization is explored along with methods of accomplishing synchronization, such as Fourier filters, adaptive filtering, in-quadrature signal generation, phase locked loops, etc. Anti-Islanding methods are discussed, as pertaining to IEEE 1547 along with maximum power point tracking algorithms, of which it is determined that the perturb and observe method along with the incremental conductance method provide the most efficiency. Finally, the concepts are combined together to simulate an H-type full-bridge inverter topology with a second order generalized integrator (SOGI) frequency locked loop (FLL) with gain optimization and a unipolar pulse-width modulated control scheme coupled with a maximum power point tracking (MPPT) control block and algorithm driving a DC-DC step down converter. Simulations verify the concepts discussed and establish a concise text regarding a complete utility interactive inverter system.

### INTRODUCTION

For hundreds of years, the use of fossil fuels have significantly shaped our lives, from the generation of electricity to the internal combustion engine that powers the automobiles we drive every day. Fossil fuels have brought about tremendous changes in the world as evident by the Industrial Revolution, which provided advancements in manufacturing, agriculture, and technology to name a few. These advancements have had a profoundly positive impact on human society as more job opportunities were available than ever before and a global economic infrastructure began to take shape as a result of mass production and transportation capabilities. However as technology has progressed, so has our understanding of the negative consequences from the use of fossil fuels.

According to a US Environmental Protection Agency (EPA) report released in 2011, almost 95% of the greenhouse gases that were generated in the United States in 2009 were due to the combustion of fossil fuels [1]. The results of this and many other similar studies have raised our awareness of the detrimental impact that the combustion of fossil fuels have on our environment and our health. This has provided a shift in our way of thinking, as now we assess the results of our actions and how they will affect our environment. In recent years, legislation has been passed to further our advancement and use of technologies utilizing renewable energy sources, such as wind, heat and sunlight.

As we now strive to become an environmentally friendly society, more and more companies and institutions are developing new technologies, and improving existing technologies, to take advantage of renewable energy sources. One such technology is the use of solar panels to generate electricity. Solar panels are able to accept sunlight and convert that energy into electricity, thus providing a viable energy source devoid of the harmful effects from the combustion of fossil fuels.

The production of electricity from the use of solar cells is nothing new. In fact, in 1839 French physicist A.E. Becquerel was the first to discover the photovoltaic effect while studying the effect of light on electrolytic cells. Little did he know that his discovery would eventually propel the human race into a new technological frontier and provide the means to power satellites and vehicles sent into orbit to explore the depths of our solar system and universe. However, as revolutionary as his discovery was, it was not until 1954 at Bell Laboratories when the first modern photovoltaic cell was developed. From that point on we have seen solar cells be utilized in anything from small electronics, such as calculators, to large scale solar panel installations capable of generating upwards of a few hundred megawatts (MW) of electricity. In fact, at the time of this writing, California State University Northridge has installed solar array systems in two areas of the campus with a total system size of 872 kW DC. Also, since its inception in March

2005, the solar array has generated over 10 megawatt-hours (MWh) of energy, enough energy to power over 206,000 homes for one day.

The use of solar panels for the generation of electricity is not limited only to large organizations such as energy companies or educational institutions. Due to advancements in technology and the public's awareness of the availability of such technologies, many home owners have installed solar panels on the roofs of their homes to generate their own electricity and thus reduce their energy costs and reduce the amount of fossil fuels consumed by power plants. Some governments even offer incentives and rebates for home owners who install such panels on their homes.

As a result, the quantity of solar panel installations throughout the world has tremendously increased in recent years. This has in turn caused many startup companies to emerge in order to provide the hardware and installation services of solar panel systems. As we see a proliferation of solar panel installations, the engineering community must be able to provide the technology that will accommodate the needs of the different types of consumers of these photovoltaic systems.

For example, a residential installation of a solar panel system would have to allow for both a stand-alone system and one that is going to be grid connected, which will be able to feed any unused energy back into the system. This will also hold true for commercial installations, however, these installations must be able to provide 3-phase power, as opposed to single phase power found in residential installations. These and other issues such as anti-islanding, synchronization, etc. will be touched upon along with a general introduction to photovoltaic systems and their properties.

However, no matter the type of system to be designed and installed, one piece of hardware is essential to the proper operation of the photovoltaic system, the inverter. The inverter is one of the most important components of the system and its proper operation is crucial to the efficiency and feasibility of the solar panel installation. Its most fundamental operation is to transform the direct current (DC) generated by the solar cells into alternating current (AC) that is used in ALL residential and commercial buildings as its electrical power source, which we will discuss in further detail.

We will focus on all aspects of the inverter as it applies to grid connected/utility interactive applications. Basic photovoltaic theory will be introduced to set a foundation in regards to the spirit of this text, along with general engineering concepts that will be needed for a complete understanding. Power electronics, in relation to the inverter, will be heavily relied upon and topics related to photovoltaic systems, such as Maximum Power Point Tracking (MPPT), utility synchronization and anti-islanding techniques will

be explored. The motivation behind this project is to provide a unified source of information regarding photovoltaic theory and its application in utility interactive inverter technology.

### PHOTOVOLTAIC THEORY

### Introduction

The photovoltaic effect, as stated previously, was discovered in the 19<sup>th</sup> century; and since then, advancements in science and technology have enabled us to successfully harvest solar energy from our sun and convert it into electrical energy capable of powering the appliances and devices we use on a daily basis. The mass production of semiconductors, using elements such as silicon, has no doubt contributed to the proliferation of solar cells in the market, considering that the semiconductor material is the fundamental component of the cell and photovoltaic theory. As such, to further explore the subject of photovoltaics, we must first establish an adequate understanding of the science involved.

Sunlight is a form of electromagnetic radiation (EMR), that is, energy with both an electric and magnetic field component that travels in a wave-shaped pattern through space. The basic unit of EMR, and thus sunlight, is a mass-less, charge-less elementary particle called the photon. Since EMR has been proven to travel in a wave-like pattern, so must the photon. Also, all wave-like patterns have an associated wavelength,  $\lambda$ , and the photon is no exception. Since the photon is mass-less, its energy is dependent only upon its wavelength, which can be shown as

(1)

$$E_{\lambda} = \frac{hc}{\lambda}$$

where *h* is Planck's constant (6.62606957 x  $10^{-34}$  J·s or 4.135667516 x  $10^{-15}$  Ev·s), *c* is the speed of light/photon (299792458 m/s) and  $\lambda$  is the wavelength of the photon. For example, the energy of a photon with a wavelength of 700nm (visible light of the color red) is approximately 1.39 x  $10^{-31}$  J·s or 1.77 Ev·s. The importance of Equation (1) is realized in the fact that only photons with energy greater than the semiconductor band gap ( $E_G$ ) will contribute to the energy conversion process. This energy must be enough to form an electron-hole pair in the semiconductor material. As such, the spectral nature of sunlight is an important consideration in the design of efficient solar cells. We will explore the semiconductor band gap further in the text.

The creation of multiple electron-hole pairs in the semiconductor generates an electrical current between n-type and p-type materials, due to the simple fact that electrons and holes are carriers of electrical current. To compare this process to a familiar electrical process and facilitate a general understanding, the semiconductor can be thought of as a diode that allows the passage of electrical current through its terminals in a particular

direction, after it has absorbed the energy of sunlight and converted into an electrical current. Figure 1 shows the structure of a conventional solar cell and also demonstrates the energy conversion process.

**Figure 1** A conventional solar cell. Creation of electron-hole pairs, e<sup>-</sup> and h<sup>+</sup>. Generated current flows between the metal grid and metal contact, which are opposite in polarity due to the migration of electrons and holes

Since the energy conversion process in the solar cell is highly reliant upon the energy available in sunlight, we must analyze the spectral irradiance of sunlight. The surface temperature of the sun is measured to be 5762 K and its radiation spectrum is closely approximated to that of a black-body radiator, a physical body that absorbs all wavelengths of incident electromagnetic radiation. Also, the emission of radiation from the sun, along with all black-body radiators, is isotropic, that is, it radiates uniformly in all directions. However, due to the fact that the Earth is such a great distance away from the sun (almost 150 million kilometers), only those photons emitted directly in the direction of the Earth will contribute to the solar spectrum as observed from the Earth. Since the atmosphere affects the spectral content and intensity of the radiation reaching Earth's surface from the sun, we must be able to measure this effect. This measurement is known as the Air Mass number and can be calculated by the following equation

(2) Air Mass =

$$\frac{1}{\cos\theta}$$

where  $\theta$  is the angle of incidence ( $\theta = 0$  when the sun is directly overhead). An Air Mass number of 0 (AM0) is the spectral distribution just above the Earth's atmosphere. AM1.5 is a widely used standard used to compare solar cell performance that is normalized to a total power density of 1 Kw/m<sup>2</sup>. The Air Mass number can be further defined in terms of whether or not the measured spectrum includes the diffuse component, such as when we observe the spectral content of sunlight from here on Earth due to the reflection and scattering in the atmosphere and surrounding landscape. For example, an Air Mass number of AM1.5d signifies that the measured spectrum does not include the diffuse component and is therefore direct, whereas AM1.5g signifies a global measurement that includes the diffuse component.

Figure 2 The radiation spectrum for a black-body at 5762 K, an AM0 spectrum, and an AM1.5 global spectrum [2]

As we can see in Figure 2, a  $100 \text{ cm}^2$  surface area (the area of a typical solar cell used on a solar array panel) of sunlight on the Earth's surface can have an incident power up to

approximately 175 kW at approximately the 500 nm wavelength. However, we are well aware that a real-world solar cell will not produce power anywhere near the amount we observe in Figure 2. As such, we must explore the underlying operation of solar cells and to do so, we must understand some fundamental properties of semiconductors which will lead us to define the most basic attributes of the solar cell: the open-circuit voltage,  $V_{OC}$ ; the short-circuit current,  $I_{SC}$ ; the fill factor, FF; the conversion efficiency,  $\eta$ ; and the collection efficiency,  $\eta_c$ .

### **Semiconductors**

The discovery of semiconductors have allowed for some of the greatest technological advances in history. As shown earlier, the characteristics of semiconductors are ideal for their use in solar cells. The most common semiconductor material used in the fabrication of solar cells is silicon (Si), whether it be crystalline, polycrystalline, or amorphous. Although there are other materials such as GaAs, GaInP, and CdTe that can also be used, silicon has been the most common choice due to the fact that its absorption characteristics are a good match to our solar spectrum [2]. We will only provide the essential concepts of semiconductors as related to this paper. A more in depth analysis of semiconductors can be explored through sources [2, 5, 6], or others, if further explanation of the introductory material is required.

It was stated earlier that in order for the energy conversion process in semiconductor materials to occur, absorbed photons must have an energy greater than the semiconductor's band gap  $(E_G)$ . The material's band gap is essential to the solar energy conversion process. The best way to understand the energy conversion process, and consequently the band gap, is to analyze how electrons behave and essentially what it takes to get those electrons excited. Electrons carry a negative charge, and when a large number of electrons move in the same direction, they form an electric current. Borrowing from quantum mechanics, electrons in an atom can be thought of as being somewhere in an array of possible "states" – which include their energy level, momentum and spin – with different probabilities of being in a given state. Two electrons cannot be in the same state at the same time; at least one of the aforementioned variables must be different. Some particular states are possible, and some are forbidden by the laws of quantum mechanics. Sets of possible states form regions that are called bands. Set of states that are not possible form regions between those bands, and these are called band gaps. In order to create electrical current in the semiconductor material, enough energy is needed to excite the electrons to move between the bands, and thus, through the band gap. Figure 3 illustrates this concept by plotting the energy E versus the crystal momentum p. Materials with a fairly large band gap are referred to as *insulators*. The

large band gap between the valence and conductions bands of insulators prevent electrons from reaching

**Figure 3** A simplified energy band diagram at T > 0 K for a direct band gap ( $E_G$ ) semiconductor [2]

the conductions at ordinary temperatures, such as what we experience here on Earth. *Conductors*, on the other hand, have overlapping bands with no band gap, which means that their electrons are essentially free to move from the valence band to the conduction band. As one can already imagine, semiconductors can act as both insulators and conductors directly due to their band gap. At lower energy levels, semiconductors will not conduct electricity, whereas at higher energy levels, the semiconductor behaves like a conductor in its electrical characteristics.

As we are well aware, different materials have different characteristics, and semiconductors are no exception. Semiconductors have two different types of band gaps: *direct band gaps*, as seen in Figure 3, and *indirect band gaps*. The difference between the two is actually quite simple. When the minimum of the conduction band and the maximum of the valence band occur at the same value of the crystal momentum, as shown in Figure 3, the material is considered a *direct band gap* semiconductor. When they do not align, then the semiconductor is said to be an *indirect band gap* semiconductor. Si is an indirect band gap semiconductor, whereas CdTe or GaAs, for example, are direct band gap semiconductors. One can deduce from Figure 3 that direct

band gap materials are a much better candidate for solar cell fabrication compared to indirect band gap materials as they will absorb light better due to the amount of energy needed to move electrons between bands. However, Si, an indirect band gap semiconductor, is the most common material used to make solar cells. This may be attributed to the availability and cost of production of Si compared to other semiconductor materials. As stated previously, a more in-depth analysis can be attained through sources [2, 5, 6] and others.

Figure 4 depicts the structure of a simple solar cell to assist in attaining the fundamental properties of a solar cell pertaining to photovoltaic energy production: the short-circuit current, open circuit voltage and the fill factor.

Figure 4 Simple solar cell structure used to analyze the operation of a solar cell. Free carriers have diffused across the junction (x = 0) leaving a space-charge or depletion region practically devoid of any free or mobile charges. The fixed charges in the depletion region are due to ionized donors on the n-side and ionized acceptors on the p-side [2]

During the solar energy conversion process, electrical current flows through the solar cell's terminals at  $x = W_P$  and  $x = -W_N$ . Without exhausting the derivation, a solar cell's short-circuit current can be defined as

$$(3) \quad I_{SC} = I_{SCN} + I_{SCD} + I_{SCP}$$

where  $I_{SC}$  is the short-circuit current and is the summation of the short-circuit current from each of the three regions: the *n*-type region ( $I_{SCN}$ ), the depletion region ( $I_{SCD}$ ), and the *p*-type region ( $I_{SCP}$ ). By observing Figure 4, this conclusion can be made rather easily, however, a full mathematical derivation of equation (3) is outside the scope of this paper and can be found in [2]. We can furthermore represent the solar cell as an electrical circuit model, as shown below in Figure 5.

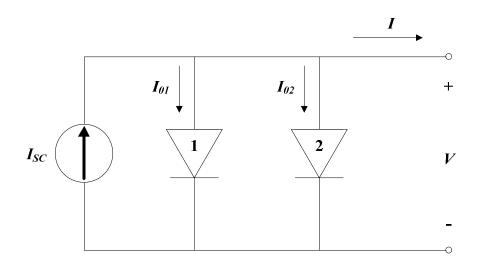

Figure 5 A simple solar cell circuit model. Diode 1 represents recombination in the quasi-neutral region, while diode 2 represents the recombination in the depletion region

Please note that for ease of discussion, we have not included parasitic series and shunt resistances inherent in real-world solar cells. As such, this is considered an idealized model of a typical solar cell. Using elementary circuit analysis and derivations shown in [2], we can represent the circuit model in Figure 5 with the following equation:

(4)

$$I = I_{SC} - I_{01} (e^{qV/kT} - 1) - I_{02} (e^{qV/2kT} - 1)$$

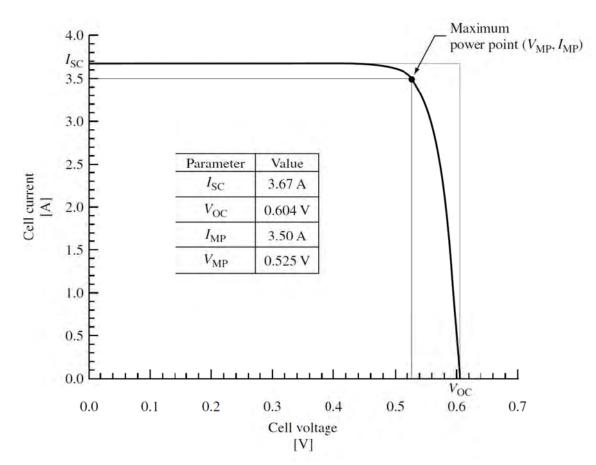

where  $I_{01}$  is the dark saturation current due to recombination in the quasi-neutral regions,  $I_{02}$  is the dark saturation current due to recombination in the depletion (space-charge) region, q is the magnitude of the charge of an elementary electron, k is Boltzmann's constant, and T is the temperature in Kelvin [2]. A common and reasonable assumption for a good silicon solar cell is the elimination of diode 2, the dark saturation current due to the depletion region. This model, along with derivations made in [2], allows us to plot the current-voltage characteristic of a given silicon solar cell in Figure 6.

This plot illustrates the important characteristics of the solar cell: the short-circuit current, the open-circuit voltage, and the fill factor. When the applied voltage, V, is small, the diode current is negligible and current can be approximated to the short-circuit current,  $I_{SC}$  (set V = 0 in equation (4)). Conversely, when the applied voltage is high enough that the recombination current (diode current) becomes significant, the solar cell current,  $I_{SC}$ , quickly drops to zero.

Figure 6 Current-voltage characteristic of a typical silicon solar cell [2]

In an open-circuit condition (I = 0), all of the light-generated current,  $I_{SC}$ , is flowing entirely through diode 1, and thus, the open-circuit voltage,  $V_{OC}$ , can be written as

(5)

$$V_{OC} = \frac{kT}{q} ln \frac{I_{SC} + I_{01}}{I_{01}} \approx \frac{kT}{q} ln \frac{I_{SC}}{I_{01}}$$

where  $I_{SC} >> I_{01}$ . Please turn your attention to the "knee point" of the curve shown in Figure 6. This point is where the power produced by the solar cell is at a maximum. This is referred to as the *maximum power point*,  $P_{MP} = V_{MP}I_{MP}$ . We will discuss in depth the use and calculation of the maximum power point in regard to inverters later in the text. Of particular interest is the rectangle whose area, given by  $P_{MP}$ , is the largest rectangle for any point on the *I-V* curve shown in Figure 6. The maximum power point is found by solving the following equation:

(6)

$$\left. \frac{\partial P}{\partial V} \right|_{V=V_{MP}} = \left. \frac{\partial (IV)}{\partial V} \right|_{V=V_{MP}} = \left[ I + V \frac{\partial I}{\partial V} \right] \right|_{V=V_{MP}} = 0$$

The current at the maximum power point,  $I_{MP}$ , is then found by evaluating equation (4) at  $V = V_{MP}$ .

The fill factor, FF, is a measure of the "squareness" of the *I*-V characteristic curve in Figure 6, is always less than one, and can be defined as

(7)

$$FF = \frac{P_{MP}}{V_{OC}I_{SC}} = \frac{V_{MP}I_{MP}}{V_{OC}I_{SC}}$$

This ratio ultimately defines the actual maximum obtainable power of the solar cell. The fill factor is one of the most significant parameters in evaluating the energy yield of a solar cell, besides the efficiency.

The efficiency,  $\eta$ , of a photovoltaic cell is defined as

(8)

$$\eta = \frac{P_{MP}}{P_{in}} = \frac{FFV_{OC}I_{SC}}{P_{in}}$$

where,  $P_{in}$  is the *incident power* determined by the properties of the light spectrum incident upon the photovoltaic cell. Information regarding the experimental determination of said properties can be found in [2].

The last attribute of the photovoltaic cell we will discuss is the collection efficiency,  $\eta_C$ . A solar cell's collection efficiency is a measure of how well the cell is able to convert energy received from photons into electrical current. The collection efficiency can be defined in two ways: the external efficiency,  $\eta_C^{ext}$ , defined relative to both optical and recombination losses, and the internal efficiency,  $\eta_C^{int}$ , defined with respect to recombination losses only. The external collection efficiency can be calculated with the following equation

(9)

$$\eta_C^{ext} = \frac{I_{SC}}{I_{ph}}$$

where

(10)

$$I_{ph} = qA \int_{\lambda < \lambda_G} f(\lambda) d\lambda$$

is the maximum possible photocurrent that would result if all photons with  $E > E_G (\lambda < \lambda_G)$ =  $hc/E_G$ ) created electron-hole pairs that were collected. A is defined as the area of the solar cell and  $f(\lambda)$  is defined as the photon flux shown in [2]. The internal collection efficiency can be calculated with the following equation

(11)

$$\eta_C^{int} = \frac{I_{SC}}{I_{gen}}$$

where

(12)

$$I_{gen} = qA(1-s) \int_{\lambda < \lambda_G} [1-r(\lambda)]f(\lambda) (1-e^{-\alpha(W_N+W_P)}) d\lambda$$

is the light generated current, *s* is defined as the grid-shadowing factor,  $r(\lambda)$  is defined as the reflectance,  $\alpha$  is defined as the reflection coefficient,  $W_N$  is defined as the width of the n region, and  $W_P$  is defined as the width of the p region [2]. This would represent the short-circuit current if every photon that is absorbed by the solar cell is collected and contributes to the short-circuit current. It should be noted that the average solar cell is only 10% efficient.

The characteristics discussed above are just the fundamental properties of photovoltaic theory and are presented to provide the required material necessary for proper comprehension of the subject. There is more information that may need to be explored for accurate system design, however, that would be beyond the scope of this paper. Please refer to [2] for further in-depth information regarding cell manufacturing, theoretical limits of photovoltaic conversion, semiconductor composition and other important topics regarding photovoltaic theory.

### A Complete Photovoltaic System

Departing momentarily from theory, let us take a more practical approach in understanding the photovoltaic system as a whole, as it pertains to our daily lives. We now have some knowledge pertaining to the solar cell and its major characteristics. Our next task is to apply this knowledge and benefit from the results.

Let us consider a single family home containing 4 family members. In the United States, the average energy consumption is 12000 kWh/person/year. However, this includes all the energy required at work, school and the energy required to produce goods purchased by each person. Therefore, if we assume that, on average, the energy consumption percapita at home is one-third of the average energy consumption, we can conclude that energy consumption at the home is 4000 kWh/person/year. Dividing by 365 days a year and multiplying by 4 members of the single family we have approximately 44 kWh/day

of energy consumption. We must now determine the size of the photovoltaic array to be installed, along with an adequately sized inverter to convert the DC generated by the solar panel(s) into AC used throughout the home. Other considerations such as conductor sizing, circuit protection, etc. will be omitted in this paper but must be considered at the time of system design.

According to [3], solar irradiance has been measured to be 1.3608 kW/m<sup>2</sup> and thus the daily value of solar energy per square meter in terms of kilowatt hours is approximately 32.66 kWh/m<sup>2</sup>. Given the fact that the average photovoltaic cell is only 10% efficient, this value becomes 3.266 kWh/m<sup>2</sup>/day. Therefore, for an average single family home consisting of 4 members, the size of the required photovoltaic array would approximately be 13.5 m<sup>2</sup> (145 ft<sup>2</sup>), which the average household roof can more than accommodate for.

Now to calculate the size of the inverter required, we must take into account that on average, present day inverters are 90% - 95% efficient, because some of the power is lost as heat during the conversion process. Therefore, if we divide 44 kWh/day by 24 h/day we will have approximately 1.83 kW, and taking into account a 90% efficiency rating of the inverter, we must install an inverter rated at least 2 kW.

Typically, the input voltages of inverters are between 140 VDC and 450 VDC, with 500 VDC being the maximum input voltage allowable. The output voltage of our panel(s) will vary throughout the day, each day, and will also vary with temperature. We must ensure that the total open-circuit voltage of the installed panels does not exceed the maximum allowable input voltage of the inverter.

Advances in technology and the photovoltaic cell fabrication process have led to the production of cells that are able to provide a much higher output in power than compared to the example shown in Figure 6, sometimes providing twice the maximum power point current under standard test conditions, STC (1 kW/m<sup>2</sup>, 25°C, AM 1.5) [4]. Let us consider a typical 156mm x 156mm (6.14 in x 6.14 in) monocrystalline silicon cell used in many photovoltaic panels today. Each cell has the following specifications as shown in Table 1.

We can construct a solar module capable of producing 200 W by connecting together 50 monocrystalline silicon cells, whose specifications are shown in Table 1.

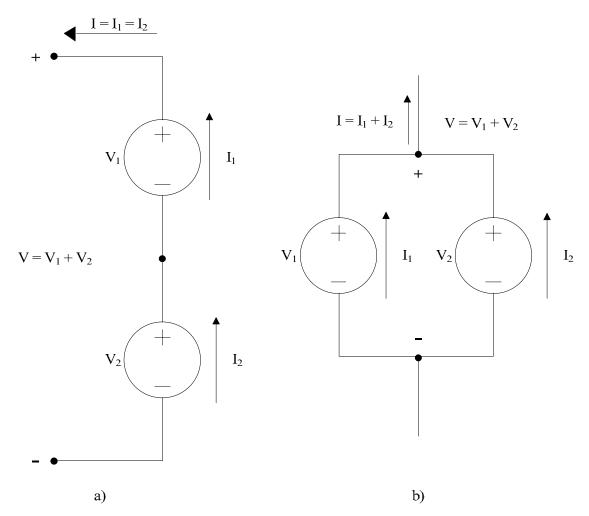

There are two ways to connect solar cells, as there are two ways to connect any electrical components together, in series or in parallel, as shown in Figure 7. Connecting cells in series effectively adds the output voltage of each cell, and in the same way, connecting cells in parallel adds the output current of each cell.

| Parameter                                | Value   |

|------------------------------------------|---------|

| Maximum Power Rating (P <sub>MAX</sub> ) | 4 W     |

| Open Circuit Voltage (V <sub>OC</sub> )  | 0.616 V |

| Short Circuit Current (I <sub>SC</sub> ) | 8.60 A  |

| Maximum Power Voltage (V <sub>MP</sub> ) | 0.496 V |

| Maximum Power Current (I <sub>MP</sub> ) | 8.07 A  |

Table 1Specifications of a typical 156mm x 156mm monocrystalline silicon cell at STC (1 Kw/m², 25°C, AM 1.5)

Figure 7 Solar Cell Connection a) Series Connection of Solar Cells b) Parallel Connection of Solar Cells

For simplicity, and to follow the convention of most photovoltaic module manufacturers today, let us construct a solar module by connecting 50 individual photovoltaic cells in series, as shown in Figure 8.

Figure 8 Electrical representation of a photovoltaic module with 50 series connected solar cells

As such, the module in our example will have the following specifications shown in Table 2 below. The dimensions of this module are  $1.658 \times .834 \times .046m (5.44 \times 2.74 \times .151 \text{ ft})$ , which corresponds to a surface area of  $1.383 \text{ m}^2 (14.89 \text{ ft}^2)$ .

| Parameter                                | Value  |

|------------------------------------------|--------|

| Maximum Power Rating (P <sub>MAX</sub> ) | 200 W  |

| Open Circuit Voltage (V <sub>OC</sub> )  | 30.8 V |

| Short Circuit Current (I <sub>SC</sub> ) | 8.6 A  |

| Maximum Power Voltage (V <sub>MP</sub> ) | 24.8 V |

| Maximum Power Current (I <sub>MP</sub> ) | 8.07 A |

**Table 2** Specifications of a typical 50 cell photovoltaic module at STC (1 kW/m², 25°C, AM 1.5) [7]

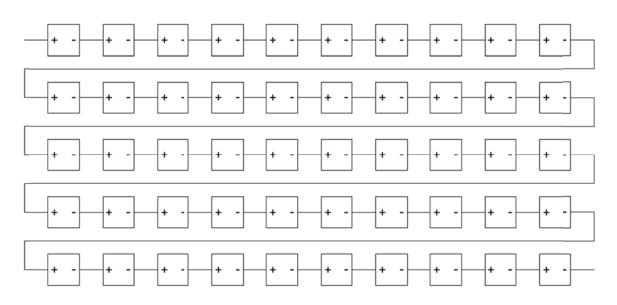

To provide the average household of 4 with 1.83 kW of power, we will need to connect 10 of these photovoltaic modules in series, to create a photovoltaic array with the ratings shown in Table 3.

| Parameter                                | Value  |

|------------------------------------------|--------|

| Maximum Power Rating (P <sub>MAX</sub> ) | 2 kW   |

| Open Circuit Voltage (V <sub>OC</sub> )  | 308 V  |

| Short Circuit Current (I <sub>SC</sub> ) | 8.6 A  |

| Maximum Power Voltage (V <sub>MP</sub> ) | 248 V  |

| Maximum Power Current (I <sub>MP</sub> ) | 8.07 A |

**Table 3** Ratings of a 10-module series array using modules with specifications shown in Table 2

This array will provide power for the 4 person household in our example and will only use  $13.83 \text{ m}^2$  (148.9 ft<sup>2</sup>) of the roof's surface area. This is strikingly close to the  $13.5 \text{ m}^2$  (145 ft<sup>2</sup>) we calculated earlier, the difference of which can be attributed to extra materials required in the fabrication process of a typical photovoltaic module. We can now construct a simple diagram for the photovoltaic system we designed for an average household of 4 people, as shown in Figure 9.

Figure 9 A simple 2 kW photovoltaic system for a typical 4 person household

As stated earlier, the reader may wish to explore in more detail in regard to photovoltaic theory and design by utilizing the sources referenced in this paper. We conclude our discussion of photovoltaics and turn to the heart of this paper, the inverter, beginning with applicable power electronics theory.

### POWER ELECTRONICS THEORY - AS IT RELATES TO THE INVERTER

### Introduction

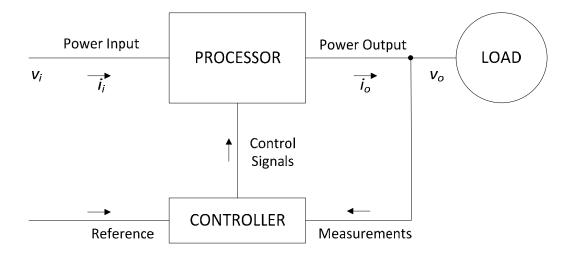

Without a minimal knowledge of power electronics theory and concepts, the task of properly identifying and understanding the operating characteristics of an inverter would be insurmountable. Power electronics can be thought of, in a general sense, as a means to supply the proper voltages and currents to a load by way of processing and controlling electric energy through a mixture of power system and electronic components. To visualize this statement, Figure 10 illustrates a block diagram of an elementary power electronic system.

Figure 10 Block Diagram of an elementary power electronic system

We can easily see that the Processor in Figure 10 accepts an incoming power signal (which may be single or three phase) and produces a suitable output power signal for the Load based on information it receives from the Controller. For example, consider that our load accepts only a DC input and the only available input source available to us is an AC source. By following the block diagram in Figure 10, the Processor could be comprised of a high-frequency transformer, rectifier circuits and filtering circuits to convert the sinusoidal AC source to a DC source suitable for the Load. By the same token, the Controller could be comprised of a microcontroller which measures the output voltages of the rectifier circuit and filtering capacitor, compares it to a reference voltage and outputs a control signal to a MOSFET that controls the output of the transformer. This is just a simple example of the application of power electronics theory.

In recent years, major advancements in the fields of microelectronics and semiconductor fabrication have allowed for more robust system design, faster processing speeds, higher

voltage and current capabilities and faster semiconductor switching speeds. This allows for broader application of power electronics from simple household rectifying transformers to utility interactive inverters and beyond.

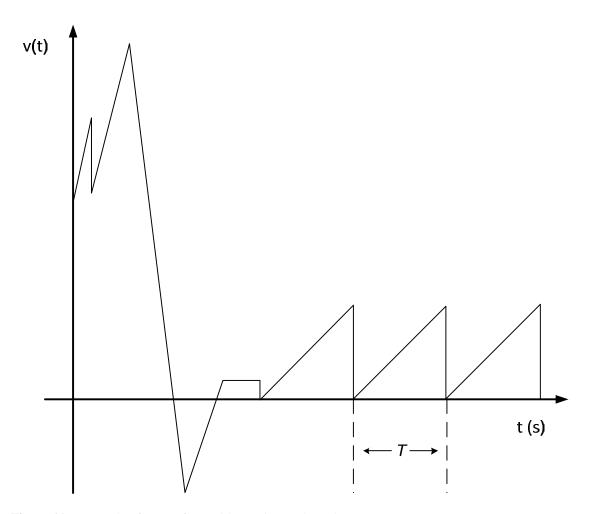

### Steady State Concepts and Fourier Analysis

Before we dive into inverter theory, let us review some fundamental concepts required for an adequate understanding. Power electronics involves circuits that contain devices, such as diodes and switches, which constantly alternate between their respective on and off states. How can one determine if these circuits are in a state of transient response or in steady state? The steady state of a circuit is the condition in which the circuit waveforms begin to repeat within a time period of T seconds. For example, Figure 11 below shows a circuit waveform in which the initial state of the circuit is of a transient nature which then settles into a steady state form, much like the response of a circuit containing reactive components changing from an off state to an on state.

Figure 11 Example of a waveform with transient and steady state responses

Now consider that we must calculate the power generated/dissipated from a given circuit or part of a given circuit. The instantaneous power flow of any given circuit can be calculated as

$$(13) \quad p(t) = vi$$

where v and i are the time varying waveforms of voltage and current respectively. This does not give us usable information about the power of the circuit because it is different for each point in time. However, if v and i repeat with a time period T in steady state, then we can calculate the average power, which is a more useful piece of information than the instantaneous power. The average power can be calculated as

(14)

$$P_{av} = \frac{1}{T} \int_0^T p(t) dt = \frac{1}{T} \int_0^T v i \, dt$$

If the circuit in question consists of a purely resistive load, then v = Ri and can be substituted in equation (14) to yield

(15)

$$P_{av} = R \frac{1}{T} \int_0^T i^2 dt$$

Let us now consider the RMS value *I* of the current, rather than the instantaneous, and express the average power as

$$(16) \quad P_{av} = RI^2$$

By comparing equations (15) and (16), we obtain

$$RI^2 = R\frac{1}{T}\int_0^T i^2 dt$$

And solving for the RMS current I yields,

(17)

$$I = \sqrt{\frac{1}{T} \int_0^T i^2 dt}$$

Examining equation (17) reveals to us the origin of RMS, as in Root Means Square. This is a general result and can be applied to all waveforms. Utilizing the same method, the RMS voltage V is determined to be

(18)

$$V = \sqrt{\frac{1}{T} \int_0^T v^2 dt}$$

By analysis, if v and i are a constant DC voltage and current, these equations would still remain valid except that the average and RMS values would be equal. Also, if the waveforms of v and i are purely sinusoidal, such as in an AC circuit, then we can calculate the RMS voltage and current to be

(19)

$$V = \frac{v}{\sqrt{2}} \quad I = \frac{i}{\sqrt{2}}$$

where v and i are the peak values of the instantaneous voltage and current waveforms respectively.

In power electronics, however, the more prevalent waveform is the nonsinusoidal waveform. This is due to the fact that most of the waveforms in power electronics are synthesized by using pieces and segments of an input waveform or waveforms. These waveforms are almost always highly distorted but are always analyzed in the steady state. As discussed earlier, the steady state waveform repeats with a time period T after an initial transient period has passed. As such, once the circuit is in steady state and the period T can be determined, the frequency of the waveform, f, can be calculated as

$$(20) \quad f = \frac{\omega}{2\pi} = \frac{1}{T}$$

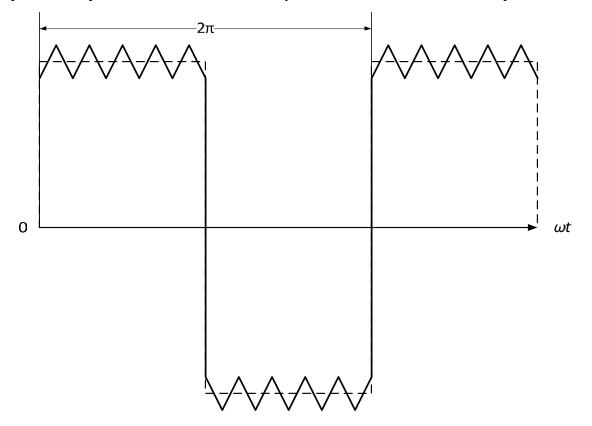

where  $\omega$  is known as the angular frequency in rad/s. The frequency f, in Hz, is known as the fundamental frequency and is usually denoted by a subscript 1. There are circuits, however, where components with unwanted frequencies may exist as a result of switching signals operating at a frequency other than the fundamental frequency, or they may be multiples, or harmonics of the fundamental frequency. These are best shown in Figure 12.

We can see that the general shape of the waveform is that of a square wave depicted by the dotted line. However, in order to obtain the square wave shape, a triangle waveform was modified to produce the square wave and the resulting unwanted components generated by the switching devices can easily be seen.

It is important to calculate these components so as to determine the total distortion present in a particular circuit. Fourier analysis is used to calculate these components.

Figure 12 Example of a nonsinusoidal waveform with multiple frequency components

In general, a nonsinusoidal waveform f(t) repeating with an angular frequency  $\omega$  can be expressed using a Fourier Infinite Series as shown below

(21)

$$f(t) = F_0 + \sum_{h=1}^{\infty} f_h(t) = \frac{1}{2}a_0 + \sum_{h=1}^{\infty} \{a_h \cos(h\omega t) + b_h \sin(h\omega t)\}$$

where

(22)

$$F_0 = \frac{1}{2}a_0 = \frac{1}{2\pi} \int_0^{2\pi} f(t)d(\omega t) = \frac{1}{T} \int_0^T f(t)dt$$

(23)

$$a_h = \frac{1}{\pi} \int_0^{2\pi} f(t) \cos(h\omega t) d(\omega t)$$

and

(24)

$$b_h = \frac{1}{\pi} \int_0^{2\pi} f(t) \sin(h\omega t) d(\omega t)$$

We can clearly see through these equations that a waveform in steady state is the sum of its Fourier components [8]. For example, a distorted waveform such as the one shown in Figure 12 can be synthesized by adding triangular waveforms at multiple pre-calculated frequencies to form the general shape of a square wave. By the same token, we can quantify the amount of distortion present in any periodic waveform by means of an index called the total harmonic distortion, or THD.

Leaving the derivation to the reader, the THD, usually shown in terms of percentage, is defined as

(25) %THD =

$$100 \times \frac{F_{dis}}{F_{s1}}$$

=  $100 \times \frac{\sqrt{F_s^2 - F_{s1}^2}}{F_{s1}}$

=  $100 \times \sqrt{\sum_{h \neq 1} \left(\frac{F_{sh}}{F_{s1}}\right)^2}$

The terms in equation (25) are all in RMS and are based under a simplifying assumption of a purely sinusoidal waveform  $F_{s1}$  at the fundamental frequency. The total waveform,  $F_s$ , is the square root of the sum of the square of  $F_{s1}$  and the sum of squares of all the waveforms containing multiples, or harmonics, of the fundamental waveform  $F_{sh}$ , where  $h \neq 1$ . The distorted waveform,  $F_{dis}$ , can be expressed as  $[F_s^2 - F_{s1}^2]^{1/2}$ .

Fourier analysis is fundamental in understanding concepts related to power electronics such as waveform shaping and calculation of total harmonic distortion (THD). It is left to the reader to further explore such topics for a more thorough understanding of Fourier analysis and its applications.

# Semiconductor Switches

The concept of switching and the use of semiconductor switches are essential to the theory, design and use of power electronic circuits. These switches allow engineers to modify voltage and current signals and route them to appropriate loads or sub-circuits. Before beginning our discussion on switches, let us briefly take into account the fundamental element of switching losses. Switching losses arise from the momentary surge in power resulting from the closing or opening of a switch. This is better described through an illustration in Figure 13.

Figure 13 Voltage, Current and Power Loss waveforms of a semiconductor switch

The operation of a switch contains three states: turn-on, conduction and turn-off. When a switch is closed and is in the turn-on state, the voltage across its terminal drops from a large value down to almost zero within a time period  $t_{on}$ . Respectively, the current rises sharply from no current to its full current value during that same time interval. This results in a temporary spike in power during the turn-on state as seen in Figure 13. After the turn-on period has elapsed, the switch is in its steady state known as the conduction state, shown by *T* in Figure 13. When the switch is opened and is in the turn-off state, the

voltage across the switch begins to rise sharply within a time period  $t_{off}$ . And as such, the current drops sharply to zero during that same time period. This turn-off state, as seen in Figure 13, also generates a temporary spike in power. The average value of the sum of these spikes is known as *switching losses* and can be calculated by

(26)

$$P_{SW} = \left(\int_0^{t_{on}} p \, dt + \int_0^{t_{off}} p \, dt\right) f_{SW}$$

where  $f_{SW}$  is the frequency at which the switch operates. The total power loss of a switch is the sum of the power loss during the conduction state and the power loss due to switching and can be shown by

$$(27) \quad P_{total} = P_C + P_{SW}$$

Calculation of these losses is essential in determining the overall efficiency of the circuit and allows engineers to determine the correct devices needed.

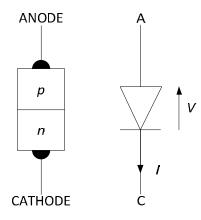

One of the most important switching devices related to power electronics and inverter design is the power diode. Power diodes are considered to be an uncontrolled semiconductor switch, in that it operates without, and independent of, a control signal. The semiconductor structure and circuit symbol of a power diode are shown in Figure 14.

Figure 14 The semiconductor structure and circuit symbol of a typical power diode

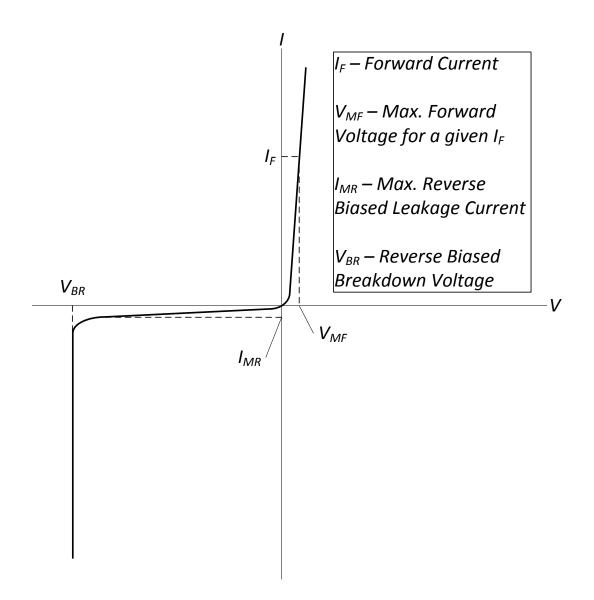

The current in a diode can only flow from anode to cathode under forward bias conditions, that is, the voltage from cathode to anode must be positive and within a certain range. Current in the reverse direction is blocked when this voltage is not positive. The voltage-current characteristic of a power diode is shown in Figure 15.

**Figure 15** Voltage-Current characteristics of a typical power diode (Different scales are used for positive and negative half-axes)

Other important characteristics of the diode such as *reverse recovery time* are left for the reader to explore. We will also forgo a discussion on semi-controlled switches, such as the thyristor family of semiconductor devices (SCRs, Triacs) and instead focus on three types of fully controlled semiconductor switches predominantly used in modern inverter systems, Power BJTs, Power MOSFETs and IGBTs. This is not to say that these three are the only devices categorized as fully controlled switches, however, they are the most prevalent in inverter systems and most applicable in terms of the scope of this project.

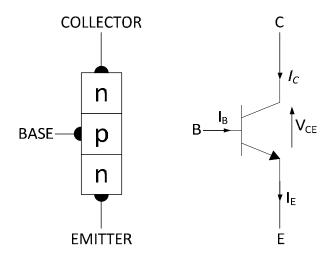

The *bipolar junction transistor* (BJT) is a three terminal semiconductor device. An npn BJT is shown in Figure 16. The collector (C) to emitter (E) path serves as the switch,

conducting or interrupting the main current, while the base (B) is the control electrode which "opens" or "closes" the switch.

Figure 16 The semiconductor structure and circuit symbol of a typical power BJT

In contrast to the thyristor family of devices not discussed in this paper, the collector current,  $I_c$ , of the BJT can be controlled continuously by the base current,  $I_B$ , as follows

$$(28) \quad I_C = \beta I_B$$

where  $\beta$  is the *DC current gain* of the transistor. This is more commonly known as a current-controlled switch and requires additional circuitry to properly bias and operate. In general, BJTs offer very low conduction losses, however, the disadvantages outweigh the advantages by a considerable margin. The voltage-current characteristics of a typical BJT are shown in Figure 17. It is important to note that in order for conduction losses to be kept to a minimum, the base current in the on-state must be high enough for the operating point to lie on, or close to, the hard saturation line associated with the lowest voltage drop across the BJT, thus resulting in the lowest power loss. Also, the BJT cannot block negative collector-emitter voltages. As such, if used in an AC-input converter, such as an inverter, the BJT must be protected from reverse breakdown with a diode connected in series with the collector. In addition, the BJT is susceptible to what is known as a *second breakdown*. The second breakdown is different from the more commonly known reverse avalanche breakdown (first breakdown) in that it occurs when both the collector-emitter voltage and collector current are high, during turn-on or turn-off states. Local hotspots appear in the semiconductor due to crystal faults, or doping

Figure 17 Voltage-Current characteristics of a typical power BJT

fluctuations, and high power losses. Throughout operation time, the temperature of these hotspots will rise ever higher and cause irreparable damage to the semiconductor. Another disadvantage of the BJT is its low current gain. As a result, multiple transistors must be used to provide a sufficient and usable current in power electronic converters. In recent years, power BJTs have been losing their market share to insulated-gate bipolar-transistors (IGBT), described later in the text. Voltage-controlled IGBTs possess all the advantages of BJTs, such as high current capability, without the weaknesses, such as second breakdown or current-controlled switching.

The power MOSFET (metal-oxide semiconductor field-effect transistor), shown in Figure 18, is best known for its high switching speed and simpler control circuitry. Also, MOSFETs have a negative temperature coefficient, which allows for paralleling transistors for increased current-handling capability along with uniform current density within the device, preventing second breakdown from occurring, as in BJTs. In addition,

Figure 18 The semiconductor structure and circuit symbol of a typical power MOSFET

the short turn-on and turn-off times of the MOSFET result in low switching losses, even at the high switching frequencies used with MOSFETs. Similar to BJTs, MOSFETs cannot be exposed to negative drain-source voltages unless protected by a diode connected in series with the transistor. The main drawback of MOSFETs, however, is the inability to carry large currents. The characteristics of the MOSFET, as seen in Figure 19, are strikingly similar to those of the BJT.

Figure 19 Voltage-Current characteristics of a typical power MOSFET

However, it should be noted that there is no hard saturation line as is present in BJTs. So the question arises, how can we incorporate the high current-handling capability of BJTs at higher switching frequencies of MOSFETs without the drawbacks of either device? The solution is the insulated gate bipolar transistor, shown in Figure 20.

Figure 20 The equivalent circuit and circuit symbol of a typical IGBT

As can be seen, IGBTs are hybrid semiconductor devices, combining the advantages of MOSFET and BJT technologies. Like MOSFETs, they are voltage controlled but have lower conduction losses and higher voltage and current ratings. The voltage-current characteristics of a typical IGBT are shown in Figure 21. There are generally two types of IGBTs, the asymmetrical and symmetrical type. The majority of IGBTs available on the market are of the asymmetrical type, that is, they do not have reverse voltage blocking capability. Symmetrical IGBTs can block reverse voltages as high as the rated forward-blocked voltage. This is a great advantage of these devices provide, however, it comes at the cost of slightly higher conduction losses when compared to their asymmetrical counterpart.

The on-state voltage drop of IGBTs is comparable to BJTs but superior to power MOSFETs. Similar to MOSFETs, IGBTs are turned on by a gate-emitter voltage around 20 V and turned off by zero voltage. Also, IGBTs can be switched with frequencies undetectable by the human ear (exceeding 20 kHz). Lastly, the maximum voltage and current ratings currently available are 6.5 kV and 2.4 kA respectively. It is because of these advantages that IGBTs are the preferred semiconductor power switch for use in modern power electronics equipment, including utility interactive inverters.

Figure 21 Voltage-Current characteristics of a typical IGBT

# The Basic Inverter

We must now develop an understanding of waveform inversion and begin to apply it in our pursuit of identifying the crucial operating requirements of the utility interactive inverter. The concept of waveform inversion is rather elementary; given a particular waveform as an input, modify that waveform into a signal that is appropriate for the load in question. For our purposes, the load in question is the 60 Hz AC waveform of the utility's electrical supply and the input waveform that needs modifying is a DC signal from a photovoltaic module. Let us begin with the most basic topology of a DC to AC inverter circuit shown in Figure 22. This topology is better known as the H-Bridge, or

Figure 22 Fundamental inverter circuit using McMurray's H-Bridge topology

Full-bridge, inverter circuit first patented by William McMurray in 1965 for the General Electric Company [9].

This simplified version of the H-bridge utilizes four (4) semiconductor switches (shown here as mechanical switches for simplicity), two on each leg (diodes are placed across the terminals of each switch to prevent a short circuit condition in the event that all switches are in the closed position. Each end of the load is tied to one of the legs between two switches. Let us assume that the load is purely resistive and that it requires an AC waveform to operate. By closing switches SW1 and SW4 in Figure 22, a positive voltage, at the value of the DC source, is created from point b to a, which results in a current flowing through the load from point a to b. Now if we open switches SW1 and SW4 and close switches SW2 and SW3, a positive voltage, at the value of the DC source, is now created from point a to b, which causes the current to flow from point b to a. This results in a negative voltage and current seen at the load. Both conditions are illustrated in Figure 23.

Figure 23 H-Bridge inverter a) positive current at load, b) negative current flow at load

By alternating this switching pattern every 0.00833 seconds, we will create an AC waveform at the load with a frequency of 60 Hz, as seen in Figure 24. Although this waveform is a square wave, it is nevertheless an AC waveform. Notice the absence of the waveforms of switches SW2 and SW4 as they only provide a path to ground, thus their respective voltages will be zero throughout the inversion process.

As discussed earlier, when dealing with waveform shaping, especially in utility interactive inverter design, care must be taken to minimize the THD of the output waveform. In the case of our basic inverter, the output we obtained was a square wave, much too different from the sinusoidal waveform we see at the utility. Using Fourier

analysis, it can be shown that a square wave is obtained through the summation of harmonic components of a sine wave. By utilizing this knowledge along with equation (25), let us calculate the %THD of the square wave we obtained from our basic inverter.

Figure 24 Voltage and Current waveforms of circuit in Figure 23

In Figure 24, we see that our output waveform has a fundamental frequency of 60 Hz. We can calculate the RMS value of the voltage using equation (18) as follows

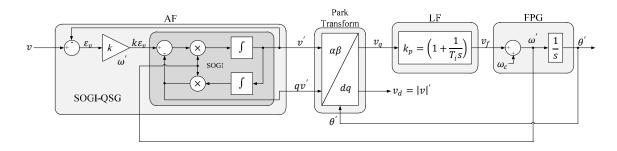

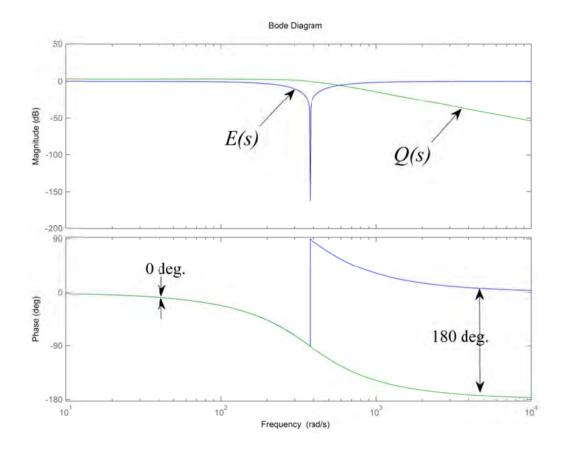

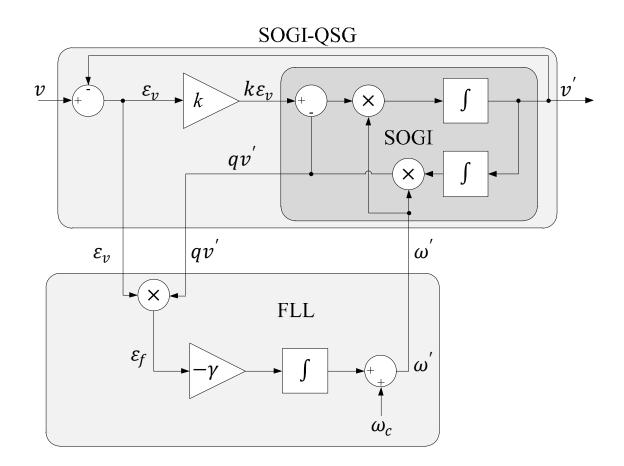

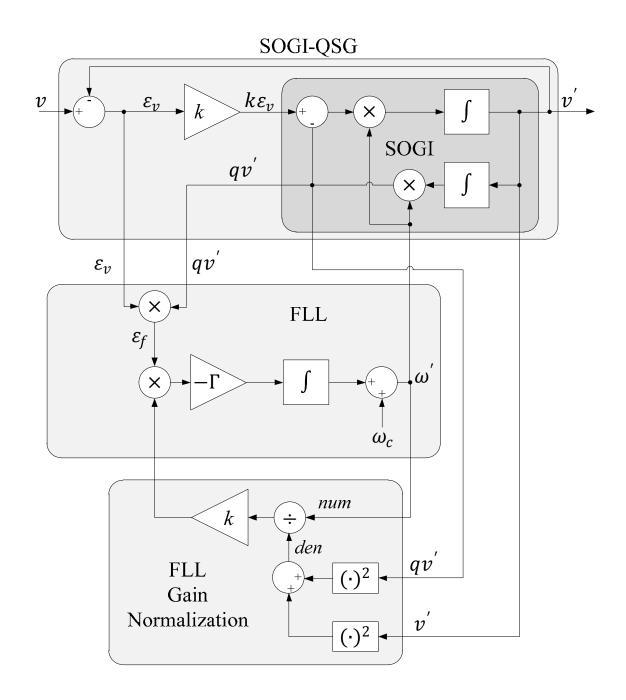

(29)