## CALIFORNIA STATE UNIVERSITY, NORTHRIDGE

## DIGITAL GRAPHIC AUDIO EQUALIZER

A graduate project submitted in partial satisfaction of the requirements for the degree of Master of Science in

Engineering

by

Alberto Luis Andres

The Graduate Project of Alberto Luis Andres is approved:

Jack Gaston

Roger M. Di Julio

Robert Y. Wong, Chairma

California State University, Northridge

## TABLE OF CONTENTS

| Approval page                        | ii    |

|--------------------------------------|-------|

| Table of contents                    | iii   |

| Abstract                             | vi    |

| Chapter 1. Basis for the design      |       |

| 1. Introduction                      | 1     |

| 2. Description and application of gr | aphic |

| equalizers                           | 2 /   |

| 3. Design requirements and approache | es 3  |

| 4. Selection of the processor        | 8     |

| 5. Basic block diagram               | 9     |

| Chapter 2. Design of the filters     |       |

| 1. Digital bandpass filters          | 12    |

| 2. Digital lowpass filters           | 29    |

| 3. Analog lowpass filters            | 35    |

| Chapter 3. Software design           |       |

| 1. Architecture and program features |       |

| of the AMI S2811                     | 41    |

| 2. Memory mapping                    | 44    |

| 3. The program                       | 48    |

| Chapter 4. Hardware design               |     |

|------------------------------------------|-----|

| 1. General architecture                  | 62  |

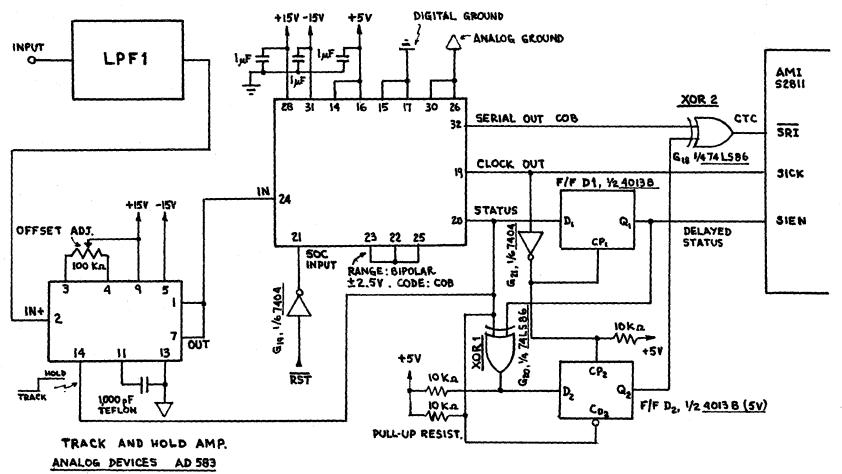

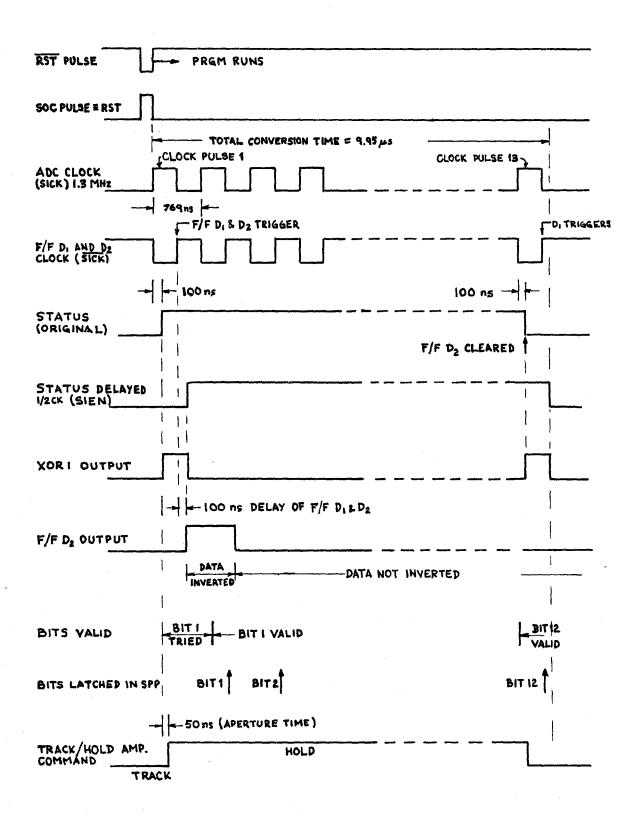

| 2. Analog to digital converter           | 68  |

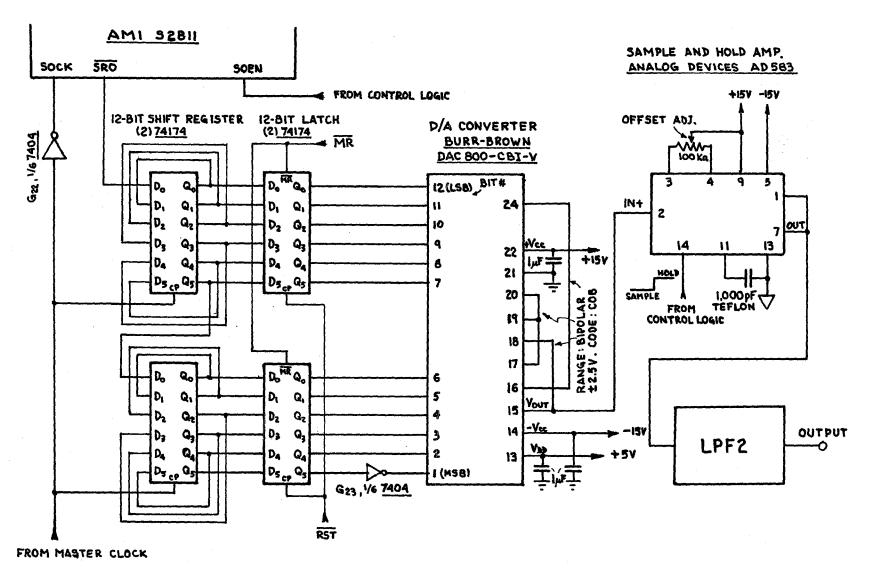

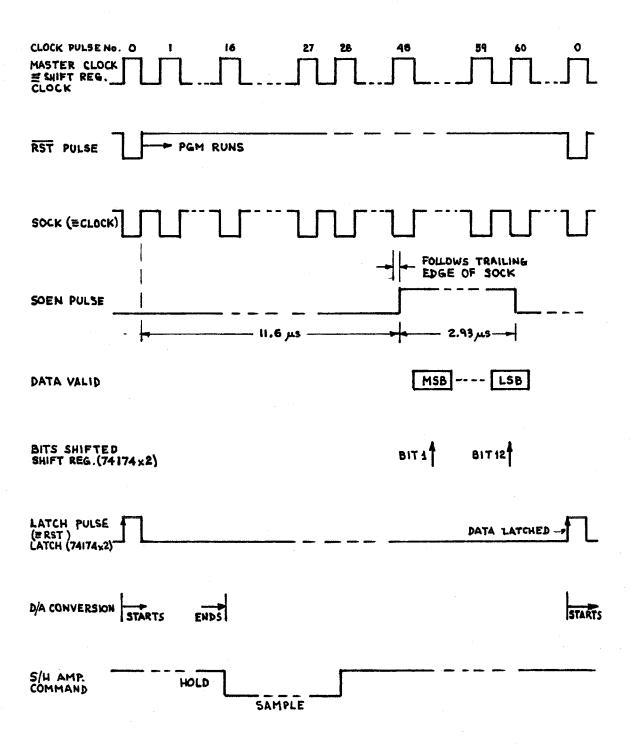

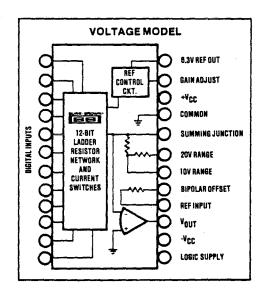

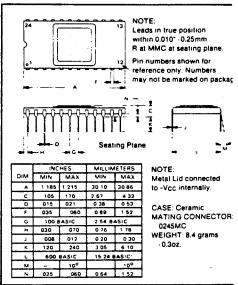

| 3. Digital to analog converter           | 75  |

| 4. Base number ROM, gain controls and    |     |

| gain coefficient ROM                     | 80  |

| Base number ROM (ROM1)                   | 80  |

| Gain controls                            | 82  |

| Gain coefficient ROM (ROM2) and          |     |

| multiplexer                              | 86  |

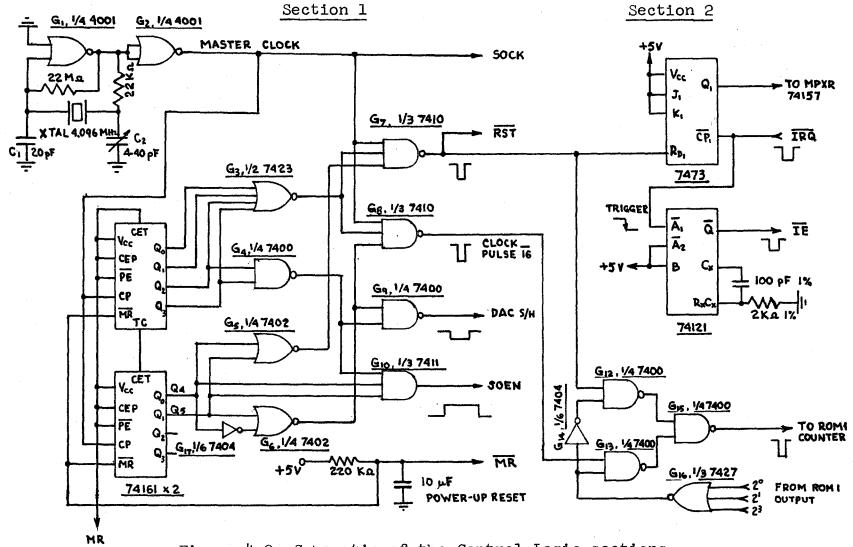

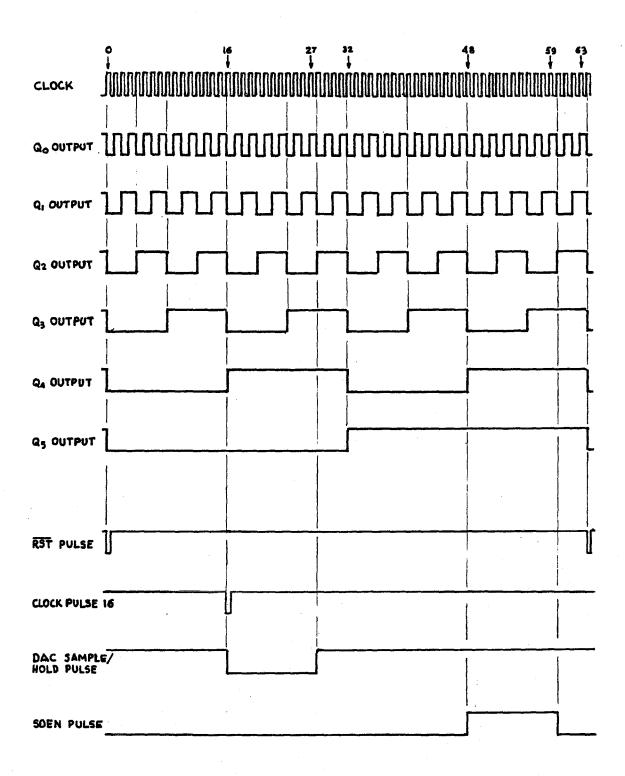

| 5. Control logic and timing              | 88  |

| Hardware implementation                  | 92  |

| ROM1 counter control                     | 96  |

| Summary and conclusions                  | 99  |

| References                               | 101 |

| Appendix                                 | 103 |

| TABLES                                   |     |

| 1.1 Sequence of filters processing       | 7   |

| 2.1 Combined output of BPF's             | 23  |

| 4.1 Addresses for decoder 74154          | 85  |

| 4.2 ROM2 addresses and gain coefficients | 87  |

# TABLE OF CONTENTS

## FIGURES

| 1.1  | Basic block diagram                        | 10 |

|------|--------------------------------------------|----|

| 2.1  | Processing sequence of BPF and LPF         | 14 |

| 2.2  | Amplitude response of a BPF                | 14 |

| 2.3  | Response of the first 6 BPF's              | 21 |

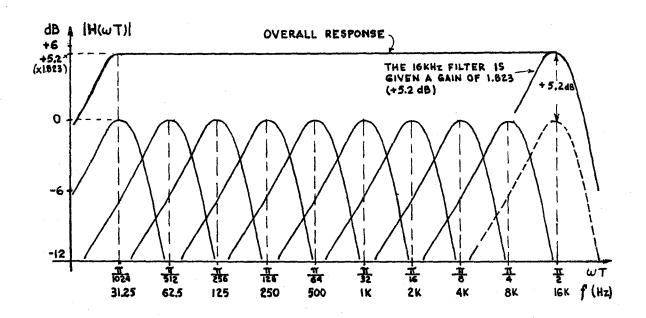

| 2.4  | Response of all the BPF's in log scales    | 21 |

| 2.5  | Poles and zeros of H(z) for BPF            | 25 |

| 2.6  | Implementation of BPF of eq. (2.12,2.13)   | 25 |

| 2.7  | Implementation of the 4th order LPF of     |    |

|      | eq. (2.19, 2.20)                           | 33 |

| 2.8  | Schematic of 4th order biquad elliptic LPF | 39 |

| 3.1  | Flow chart of the signal processing        | 45 |

| 3.2  | Memory mapping of SPP processor            | 47 |

| 4.1  | Block diagram of the complete equalizer    | 63 |

| 4.2  | Program events timing                      | 67 |

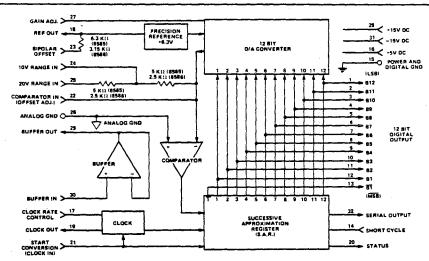

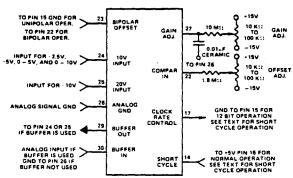

| 4.3  | Schematic of the A/D converter             | 69 |

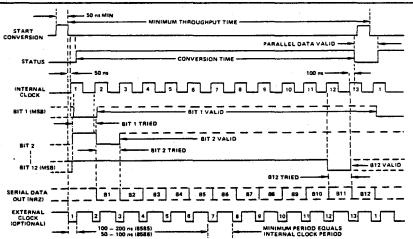

| 4.4  | Timing diagram, for the A/D conversion     | 71 |

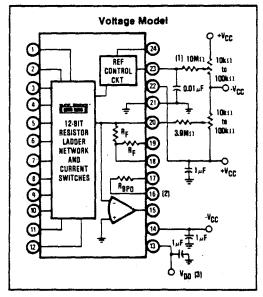

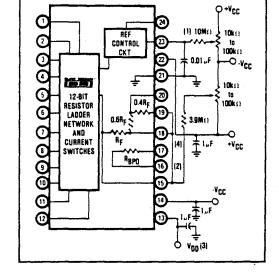

| 4.5  | Schematic of the D/A converter             | 76 |

| 4.6  | Timing diagram of the D/A conversion       | 78 |

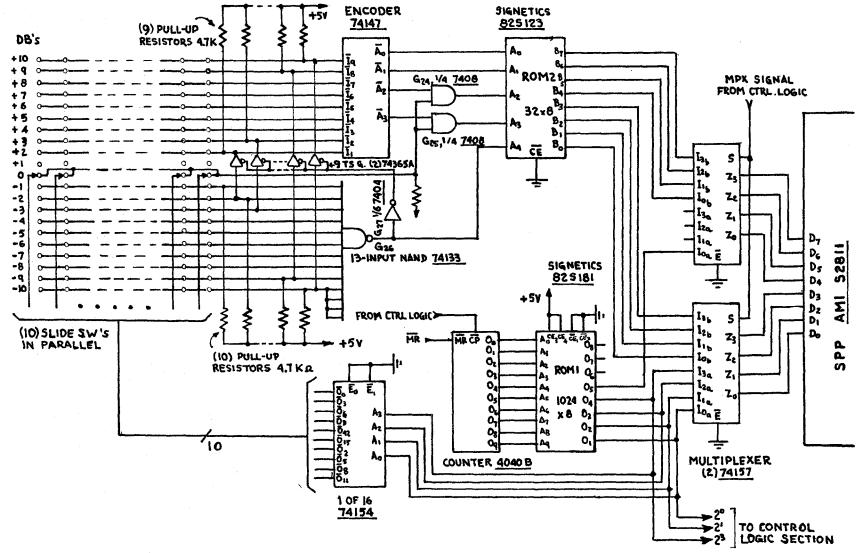

| 4.7  | Schematic of gain controls, ROM1, ROM2     |    |

|      | and multiplexer interface                  | 81 |

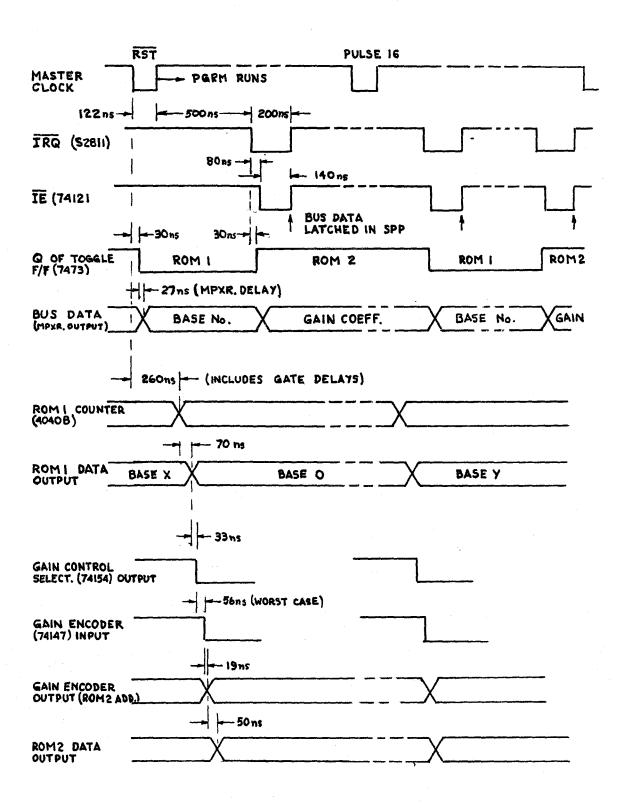

| 4.8  | Timing diagram of ROM's, Mux and Gain ctr. | 83 |

| 4.9  | Schematic of the control logic section     | 89 |

| 4.10 | Timing diagram of the control logic        | 90 |

#### ABSTRACT

## DIGITAL GRAPHIC AUDIO EQUALIZER

bу

Alberto Luis Andres

Master of Science in Engineering

Digital means are becoming common in the processing of audio signals but they have not been as yet directly utilized in home entertainment audio components due, in part, to the fast sampling rates and large dynamic ranges required for good audio reproduction. This project presents the design of an audio graphic equalizer using digital filters and signal processing. Graphic equalizers are traditionally designed with a bank of bandpass filters spaced in frequency by octaves or fractions of octaves. The design in this project uses 10 bandpass filters with frequencies related by octaves to cover the entire audio range. The system designed emphasizes the application of state of the art digital signal processing hardware to audio equipment. The

signal processor AMI S2811 is used as the heart of the system due to its fast processing speed and flexible instruction set. The speed, however, is not enough to process ten filters in a sampling period. To solve this problem, a scheme is used whereby a basic digital bandpass filter is sampled at successively halved rates to generate all the lower octave filters. Digital lowpass filters are interposed to prevent aliasing. With this scheme, only two bandpass and two lowpass filters need be processed per each sampling period. The program and hardware are designed to perform this processing and to input and output the data. The design, which has been done for 12 bit resolution, incorporates gain controls to adjust the gain of each filter so as to shape the frequency response as desired.

### CHAPTER 1

#### BASIS FOR THE DESIGN

### 1. INTRODUCTION

The objective of this project is to design an audio graphic equalizer using digital techniques. The motivating idea is to show the feasibility of designing audio equipment traditionally produced in analog form, with the presently available digital hardware. It is recognized that the necessary processing speeds have long been achieved in large computers, but only recently signal processors specially intended for audio signals have been introduced in the market at reasonable prices. Besides the relatively high speeds required for the processing of audio signals, there exists the need for large dynamic ranges.

Present day audio components can have a dynamic range of up to 80 or 90 dB. However, the dynamic range of the media used (tapes and records) is typically no more than 50 or 60 dB, or somewhat better when companding schemes are introduced. The media of the near future, instead, will offer excellent dynamic ranges. For example, digitally recorded tapes are common place in recording studios and are now being introduced in home equipment with adaptors for video recorders; the digital audio disc is now in the marketplace.

All these media have resolutions of 14 to 16 bits, what gives dynamic ranges of 84 to 96 dB using the rule of thumb that digital processing yields about 6 dB per bit. Therefore, audio processing requires large number of bits at high speeds, a combination not easy to achieve. Nevertheless, the trend is toward digital processing of audio signals and in the future, it may be expected that most components, such as preamplifiers, amplifiers, equalizers, etc., will be digital, with probably simpler and easier to interface designs.

It should be obvious that our design would be extremely costly when compared with its analog counterpart, but the purpose is to show that audio components processing signals digitally can be made with readily available hardware. The present trend in integration and cost reduction of digital parts may, in the near future, make a project like this economically competitive with today's analog designs.

## 2. DESCRIPTION AND APPLICATIONS OF GRAPHIC EQUALIZERS

Audio graphic equalizers are normally used in conjunction with other audio processing equipment, in order to compensate for deficiencies in the acoustic environment by shaping the overall frequency response of the audio system.

`Typically, the audio graphic equalizer consists of a bank of bandpass filters whose frequencies are spaced to cover the entire audio range. The audio signal is processed through all these filters and the outputs of all of them are then summed to reconstruct the original input. The level

of the signals at the output of the filters, or equivalently, the gain of the filters, can be adjusted with front panel controls so that the user can shape the frequency response of the system where the equalizer is installed to suit his requirements. A typical range of adjustment is  $\pm 10$  dB. The gain controls are usually of the slide type and placed side by side, whereby the approximate frequency response is displayed by the position of the control knobs; hence, the name of "graphic".

The frequency spacing of the bandpass filters depends on the sophistication of the equalizer but the ratio between adjacent frequencies is always an octave or a fraction of octave. For high quality, non-professional equalizers the separation between frequencies is usually an octave with 10 to 11 bandpass filters used for each channel.

## 3. DESIGN REQUIREMENTS AND APPROACHES

For a digital design, the idea is to use digital filters instead of their analog counterparts. There are many advantages to this approach. Once a design has been made, it can be easily modified for different frequencies by just changing the coefficients of the filters. Multipole, higher order filters can be easily implemented by repeated passes of the signals through second order filters or by introducing minor program changes. Furthermore, these features can be made software controllable by the user giving great flexibility in professional applications, such as in parametric equalizers.

In designing real time signal processors, such as graphic equalizers, one of the major difficulties encountered is the need for very fast arithmetic processing. A second order digital filter implementation may require 5 multiplications and 4 additions, plus possibly the multiplication of the input sample by a gain factor. In the 20 Hz-20 KHz audio range, a sampling rate higher than 40 KHz is mandatory if we are to avoid aliasing. Even though the processed audio spectrum does not normally extends up to 20 KHz, this sampling frequency may seem too low if we try to avoid highly sophisticated hardware and antialiasing filters. In any event, with only 20 to 25 usec (ideally) between samples and having to process the signal through 10 filters in that period of time, there is no conventional microprocessor in today's market capable of performing 50 multiplications, 40 additions and overhead instructions in those 20 to 25 usec.

In the case of a graphic equalizer with octave spaced filters, however, the frequencies and bandwidths of all the filters are related by powers of 2. This means that the equalizer filters are not of the constant bandwidth type but rather of the constant percentage bandwidth.

Now, the transfer function of a digital filter is defined only with respect to the sampling frequency through  $z=e^{ST}$ , where T is the sampling period,  $\underline{z}$  is the discrete complex variable and  $\underline{s}$  is the continuos complex variable. Therefore, by sampling at half the rate  $(\frac{1}{2}f_S=1/2T)$ , the

center frequency, as well as the bandwidth of the filter is halved. By processing the input to the same filter at successively halved sampling rates, we obtain precisely what we wanted: filters separated by octaves and with constant percentage bandwidth. Of course, to prevent aliasing, every time we halve the sampling rate, the samples have to be band limited to one half their previous bandwidth. This is again done with one digital lowpass filter whose cut-off frequency is halved every time the input is sampled at successively halved rates. The cut-off frequency of course, is chosen below the  $\frac{1}{2}f_{\rm S}$ , where  $f_{\rm S}$  is the sampling frequency of the corresponding bandpass filter.

For our design we decided to use 10 filters spaced in frequency by octaves and a sampling rate of 64 KHz. The processing is arranged so that the highest frequency filter, the 16 KHz, processes every sample; the 8 KHz filter processes every second sample; the 4 KHz filter, every fourth sample and so on. The 31 Hz filter processes every 512th sample. Similarly, the lowpass filter of the highest frequency (12 KHz in our case) processes every sample; the 6 KHz, every second sample and so on. (We will refer to 16K, 8K Hz filters, etc., but the filter is the same; only the sampling rate changes)

The procedure is then to pass the original signal, which has been band limited to a frequency below  $\frac{1}{2}64$  KHz (we chose 21 KHz) and which has been sampled at 64 KHz, through the 16 KHz bandpass and through the 12 KHz lowpass filters. Although the input to the 12 KHz lowpass filter is still

sampled at 64 KHz, its output can be sampled at 32 KHz by discarding every second sample, since the bandwidth has been limited to 12 KHz, i.e., below  $\frac{1}{2}f_s = \frac{1}{2}32$  KHz = 16 KHz. If this is done, that output can again be processed through the bandpass and lowpass filters at  $\frac{1}{2}f_s$ , giving outputs corresponding to 8 KHz bandpass and 6 KHz lowpass filters respectively. By continuing this process we can obtain all the other lower frequency filters.

Since every second sample is discarded, we can interleave the processing of all the filters in a sort of time division multiplexing fashion. In so doing, we realize that only two filters need to be processed per sample. For example, according to the procedure explained before, the 16 KHz filter will be processed 16 times in 16 samples; the 8 KHz, 8 times; the 4 KHz, 4 times; the 2 KHz, 2 times and the 1 KHz, once. If we were using only these 5 bands, there would be a total of 31 filters processed in 16 samples or 2 filters per sample. The same holds true for any number of bands. Therefore, all we need to do is to process two bandpass filters and two lowpass filters per sample, thus reducing our processing needs from the original 10 filters to only four.

Table 1.1 shows the sequence in which the bandpass (BPF) and lowpass (LPF) filters must be processed to interleave properly. In every sample, the first BPF is always the 16 KHz and the first LPF, the 12 KHz. Under 2nd BPF and 2nd LPF input and output are the sample numbers, with a subindex, the LPF through which the sample was processed. For example, 312

TABLE 1.1

| Samp.      | В     | PF         | 2nd BPF          | Samp.       | LPF       |            | 2nd              | LPF              |       |        |

|------------|-------|------------|------------------|-------------|-----------|------------|------------------|------------------|-------|--------|

| No.        | Proc  | essed      | Input            | freq.       | Processed |            | Processed        |                  | Input | Output |

| 1          | 16K   | 8 <b>K</b> | 112              | 32K         | 12K       | 6к         | 1 <sub>12</sub>  | 16               |       |        |

| 2          | 16K   | 4K         | 16               | 16K         | 12K       | 3K         | 16               | 13               |       |        |

| 3          | 16K   | 8ĸ         | 3 <sub>12</sub>  | 32 <b>K</b> | 12K       | 6к         | 3 <sub>12</sub>  | 36               |       |        |

| 4          | 16K   | 2K         | 13               | 8 <b>K</b>  | 12K       | 1.5K       | 13               | <sup>1</sup> 1.5 |       |        |

| 5          | 16K   | 8ĸ         | 5 <sub>12</sub>  | 32 <b>K</b> | 12K       | 6 <b>K</b> | <sup>5</sup> 12  | 56               |       |        |

| 6          | 16K   | 4K         | 5 <sub>6</sub>   | 16K         | 12K       | 3K         | <sup>5</sup> 6   | 53               |       |        |

| 7          | 16K   | 8 <b>ĸ</b> | 712              | 32 <b>K</b> | 12K       | 6 <b>K</b> | <sup>7</sup> 12  | 7 <sub>6</sub>   |       |        |

| 8          | 16K   | lK         | 1 <sub>1.5</sub> | 4K          | 12K       | 750        | 11.5             | <sup>1</sup> 750 |       |        |

| 9          | 16K   | 8 <b>K</b> | 9 <sub>12</sub>  | 32K         | 12K       | бк         | 9 <sub>12</sub>  | 96               |       |        |

| • • •      | •••   | • • •      | • • •            | • • •       | • • •     | • • •      | • • •            | • • •            |       |        |

| <b>1</b> 6 | 16K   | 500        | <sup>1</sup> 750 | 2K          | 12K       | 375        | <sup>1</sup> 750 | <sup>1</sup> 375 |       |        |

| •••        | •••   | • • •      | • • •            | • • •       | •••       | • • •      | • • •            | • • •            |       |        |

| 32         | 16K   | 250        | <sup>1</sup> 375 | 1K          | 12K       | 187        | <sup>1</sup> 375 | <sup>1</sup> 187 |       |        |

| •••        | •••   | • • •      | • • •            | • • •       | · • • •   | • • •      | •••              | • • •            |       |        |

| 64         | 16K   | 125        | <sup>1</sup> 187 | 500         | 12K       | 94         | <sup>1</sup> 187 | 1 <sub>94</sub>  |       |        |

| • • •      | •••   | • • •      | •••              | • • •       | • • •     | • • •      | •••              | • • •            |       |        |

| 128        | 16K   | 62         | 1 <sub>94</sub>  | 250         | 12K       | 47         | 1 <sub>94</sub>  | <sup>1</sup> 47  |       |        |

| • • •      | •••   | •••        | • • •            | • • •       | •••       | • • •      | • ,• •           | • • •            |       |        |

| 256        | 16K   | 31         | 147              | 125         | 12K       | <b></b>    | 147              |                  |       |        |

| • • •      | •••   | • • •      | • • •            | •••         | •••       | • • •      | • • •            | •••              |       |        |

| 512        | 16K   |            |                  | 62          | 12K       |            |                  |                  |       |        |

| •••        | • • • | • • •      | •••              | •••         | • • • •   | • • •      | • • •            | • • •            |       |        |

| 768        | 16K   | 31         | 147              | 125         | 12K       |            | 147              |                  |       |        |

|            | l     |            | Į.               | l           | Į.        |            |                  |                  |       |        |

designates the sample No. 3 after it has been processed by the 12 KHz LPF; 13 corresponds to the sample No. 1 processed by the 3 KHz LPF. All the frequencies in the table are in Hz. A few things should be noted in this table. The input to the 16 KHz BPF and 12 KHz LPF has not been indicated because it is the same for both and it is always the input sample to the processor. The input to the second BPF and LPF processed in each sample is also the same but it has been filtered by a LPF as indicated by the subindices. Note that the sequence from samples 1 to 7 repeats again from samples 9 to 15; the sequence from 1 to 15 repeats from 17 to 31 and so forth. Therefore, we have indicated only the samples where a new filter is processed for the first time in the first 512 samples. The whole sequence repeats every 512 samples. By looking at the subindices of the input sample to the second BPF and LPF, we see that the 12 appears every 2 samples, the 6 every 4, the 3 every 8, etc. At the output of the LPF, on the other hand, the 6 appears every 2 samples but every other is discarded, as discussed before; the same pattern can be observed in the other samples. As the basic sampling frequency is 64 KHz or 4 times 16 KHz, the sampling frequency for every second BPF is 4 times its frequency.

## 4. <u>SELECTION OF THE PROCESSOR</u>

Even with only 4 filters required, the processing of all of them in real time is not feasible with the speed of presently available conventional microprocessors. One

approach could be the use of high speed bit slice sections to form a dedicated computer with adequate microprogramming. Another possibility is to use the recently introduced processors that perform the operations of parallel multiplication and addition in a single execution cycle. Examples of such processors are the NEC uPD7720 and the TRW TDC1010J, which can multiply 16 x 16 bits and accumulate the result in 250 nsec and 150 nsec, respectively.

For our project, however, we have chosen the Signal Processing Peripheral (SPP) AMI S2811, from American Microsystems Inc., which has a 12-bit multiplier, but can process 16-bit input words. We chose this processor because we intended to use a 12-bit analog to digital converter which can yield an acceptable 72 dB dynamic range at a moderate price. The AMI processor can perform the multiplication and accumulation of two 12-bit words in 300 nsec. We found this speed and all the conveniences offered by the architecture and instructions set of this processor quite suitable to our requirements (see Appendix for the specifications of the S2811)

## 5. BASIC BLOCK DIAGRAM

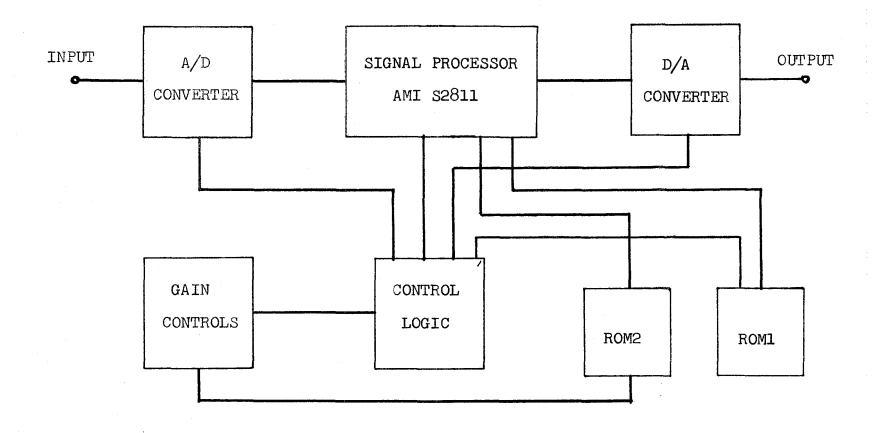

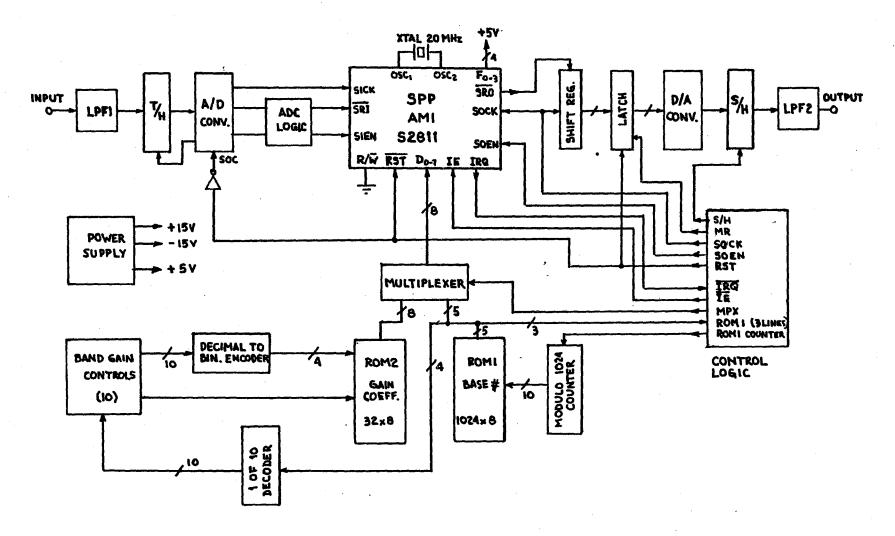

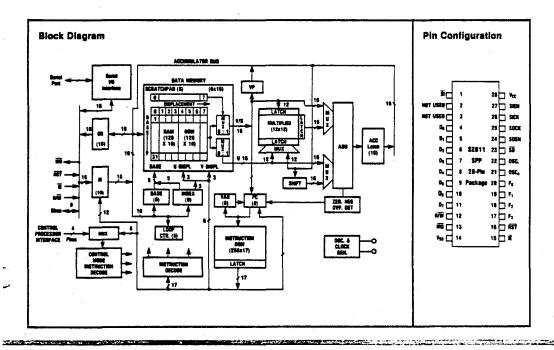

Figure 1.1 shows a basic block diagram of the equalizer. At the heart of the system is the SPP processor AMI S2811 preceded by a 12-bit Analog to Digital converter system and followed by a corresponding Digital to Analog converter system. The SPP processor has a data memory in the form of a matrix with 32 bases or rows of 8 locations each. Half of

Figure 1.1. Basic Block Diagram

the 8 locations are RAM and half are ROM. We will store the data for our bandpass and lowpass filters in these bases. The ROM1 will keep the sequence of the filter bases in the order they should be processed according to the pattern of Table 1.1. The gain controls will set the gain for each bandpass filter by addressing one of the gain coefficients stored in ROM2 at the time the corresponding bandpass filter is processed. The control logic section will keep all the portions of the equalizer system properly synchronized and will supply the necessary control signals.

#### CHAPTER 2

#### DESIGN OF THE FILTERS

## 1. DIGITAL BANDPASS FILTERS

The bandpass filters to be implemented digitally in the SPP processor AMI S2811 are of the constant percentage bandwidth type, with their center frequencies spaced by octaves from 16 KHz down to 31 Hz. As it was discussed before, a single digital filter presented with input signals sampled at successively halved rates will produce responses with successively halved center frequencies and bandwidths. When the samples are time multiplexed in the sequence explained in Chapter 1, a bandpass filter designed for a 16 KHz center frequency and appropriate bandwidth at a 64 KHz sampling rate will generate an 8 KHz, half bandwidth filter when its input is sampled at 32 KHz; a 4 KHz, quarter bandwidth when sampled at 16 KHz, and so on.

These are exactly the desired results; octave frequency spacing and constant percentage bandwidth. Therefore, only one bandpass filter (BPF) needs to be implemented for the 10 bands of the equalizer. To avoid aliasing, however, the signals are band limited with suitable digital lowpass filters every time the sampling rate is halved. Again, only one digital lowpass filter (LPF) need be implemented since its

cut-off frequency will be halved each time the sampling rate is halved.

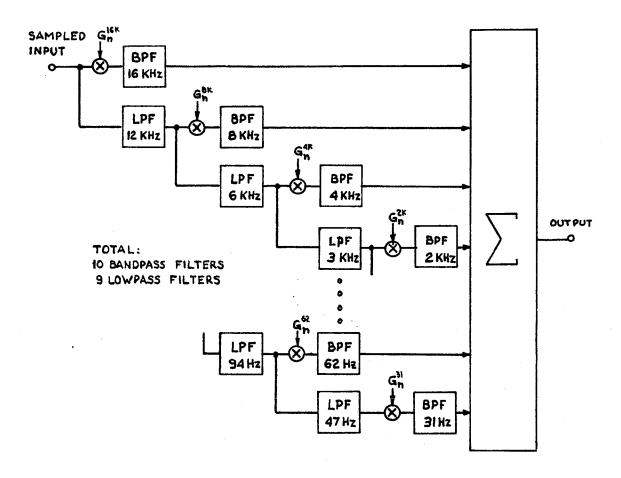

The processing of BPF and LPF is organized as shown in Figure 2.1, where the Gain coefficients, determined by the settings of the front panel band-gain controls, are also indicated.

The cut-off frequencies of the LPF have been chosen to permit the signals of interest to pass relatively unaltered while still allowing a reasonable roll-off toward the folding frequency (one half the sampling frequency). The first LPF has a cut-off frequency of 12 KHz and delivers its output to the 8 KHz BPF which processes signals sampled at 32 KHz. Therefore, the cut-off frequency of the LPF is well below the folding frequency of 16 KHz. Similarly, the rest of the LPF's have their cut-off frequencies related by octaves to the 12 KHz LPF by virtue of the successively halved sampling frequency.

Digital filters can be designed in the form of non-recursive, finite impulse response (FIR) or recursive, infinite impulse response (IIR) types. The latter are easier to implement and it is the type for which the SPP S2811 is particularly suited by reason of its architecture and programming capabilities. This is important due to the time limitations of our processing scheme. The S2811 can process a second order IIR filter in 1.5 usec, while a comparable performance FIR filter would take much longer.

Most of the digital filter design methods use a trans-

Figure 2.1 Processing sequence of BPF and LPF.

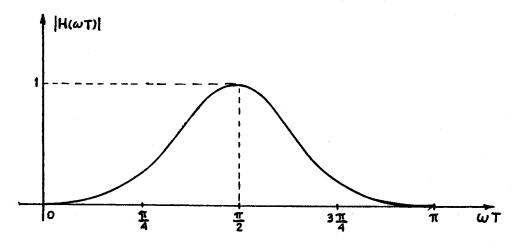

Figure 2.2 Amplitude response of a BPF.

formation from an analog, conventional type that has a performance related in some way to the desired digital filter. The transformation results in the change of a transfer function in the Laplace complex variable  $\underline{s}$  to another function in the discrete complex variable  $\underline{z}$ , with both variables being related by

$$z - e^{sT}$$

where T is the sampling period.

The impulse invariance method uses the z transform of the impulse response of the analog filter sampled at 1/T rate. The analog filter transfer function is of course, the Laplace transform of the same impulse response. With this method, therefore, the analog and digital filters have the same impulse response.

Another method is the so called matched z transformation where the poles and zeros in the  $\underline{s}$  plane are mapped directly to poles and zeros in the  $\underline{z}$  plane. Thus, for a pole or zero at s=-a there is a pole or zero at  $z=e^{-aT}$ .

Both of these methods have the disadvantage that the response of the resultant digital filter can be significant at the folding frequency if the analog filter has zeros at frequencies higher than the folding frequency. Severe aliasing may result in those cases due to the periodicity of the digital filter response. This problem is circumvented with the bilinear transformation that maps the  $\underline{s}$  plane into the z plane with the relation

$$s = C \frac{1 - z^{-1}}{1 + z^{-1}} \tag{2.1}$$

If steady state conditions are considered then  $s=j\Omega$  and  $z=e^{j\omega T}$ , that is, a unit circle in the z plane, and (2.1) takes the form

$$j\Omega = C \frac{1 - e^{-j\omega T}}{1 + e^{-j\omega T}}$$

(2.2)

where  $\Omega$  and  $\omega$  are the analog and digital circular frequencies respectively, and C is a positive constant.

The above expression can be written as

$$j\Omega = C \frac{e^{-j\omega T/2} (e^{j\omega T/2} - e^{-j\omega T/2})}{e^{-j\omega T/2} (e^{j\omega T/2} + e^{-j\omega T/2})} = C \tanh j\frac{\omega T}{2}$$

or, since tanh jx = j tan x

$$\mathbf{\Omega} = C \tan \frac{\mathbf{\omega} T}{2} \tag{2.3}$$

It is seen that the analog frequency  $\Omega$  is mapped into the digital frequency  $\omega$  through (2.3). Thus, for  $\omega$  = 0,  $\Omega$  =0 and for  $\omega = \pi/T$  (folding frequency)  $\Omega \longrightarrow \infty$ . With LPF and BPF that have zeros at infinity, the response of the corresponding digital filter is then guaranteed to be 0 at the folding frequency and no aliasing will occur even though the response will be periodic with period 2  $\pi/T$ . We choose this method of design for our digital bandpass and lowpass filters.

From the bilinear transformation of equation (2.1) we obtain with  $s = \sigma + j\omega$

$$z = \frac{C + s}{C - s} = \frac{C + \sigma + j\omega}{C - \sigma - j\omega}$$

(2.4)

It is seen that for  $\sigma < 0$ , |z| < 1 and viceversa. Then, the negative half of the <u>s</u> plane maps inside the unit circle on the <u>z</u> plane. For  $\sigma = 0$ , |z| = 1 for all values of  $\omega$  and the entire  $j\omega$  axis maps into the unit circle.

Due to the non-linear nature of the bilinear transformation, the typical method of design is to establish the critical frequencies of the desired digital filter, calculate the corresponding analog frequencies with (2.3) (prewarping of frequencies) and then find the transfer function of an analog filter that meets the response requirements at the prewarped frequencies. By applying the bilinear transformation to that transfer function, the transfer function of the matching digital filter results.

For our design, however, we shall use a different procedure starting off, somewhat arbitrarily, with a standard first order Butterworth bandpass filter and transforming it into a digital filter with the bilinear transformation. The reasoning behind this approach is that the final purpose of the audio equalizer is not to strictly separate the ten frequency bands but rather to shape the overall frequency response. Therefore, the responses of the filters are allowed to overlap and the Q of the filter is used as a parameter whose value is chosen to render a flat overall response when the magnitudes of all the filters are added together.

The transfer function of a first order Butterworth

bandpass filter in terms of the  $\underline{Q}$  and the center frequency  $\Omega_c$  is

$$H(s) = \frac{\frac{1}{Q} \Omega_c s}{s^2 + \frac{1}{\Omega} \Omega_c s + \Omega_c^2}$$

(2.5)

To apply the bilinear transformation we must determine the constant C in (2.1). One way to do this is to select a value such that a particular frequency of the digital filter matches exactly a corresponding frequency of the analog filter, with the other frequencies being related by the transformation of equation (2.3).

In our case, the sampling frequency is chosen to be 64 KHz. The highest frequency filter has a center frequency of 16 KHz and we choose to match this frequency in the analog and digital responses. Therefore, from (2.3)

$$\Omega_c = 2\pi (16 \times 10^3) = C \tan \frac{2\pi (16 \times 10^3)}{2(64 \times 10^3)}$$

from where

$$C = \Omega_c \cot \frac{\pi}{h} = \Omega_c$$

Hence, the transformation relation is

$$s = \Omega_c \frac{1 - z^{-1}}{1 + z^{-1}}$$

Substituting in (2.5) and simplifying it results

$$H(z) = \frac{1 - z^{-2}}{2Q + 1 + (2Q - 1)z^{-2}}$$

(2.6)

This is the transfer function of our digital bandpass filter. For steady state response we evaluate (2.6) on the unit circle by setting  $z=e^{j\omega T}$ . Then

$$H(\omega T) = \frac{1 - e^{-j2\omega T}}{2Q + 1 + (2Q - 1)e^{-j2\omega T}}$$

(2.7)

The magnitude response can be found by setting

$$|H(\omega T)|^2 = H(\omega T) H*(\omega T)$$

After some algebraic manipulations it results

$$|H(\omega T)| = \frac{\sin \omega T}{\sqrt{4Q^2 \cos^2 \omega T + \sin^2 \omega T}}$$

(2.8)

The amplitude response of the filter for a given Q is sketched in Figure 2.2 as a function of the normalized digital frequency  $\omega T = \omega/f_S$ , where  $f_S$  is the sampling frequency. The response for all the other 9 filters will be identical to this one, as explained before, since for every octave the sampling period will be multiplied by a factor  $N = 2^k$  and the frequencies will be correspondingly divided by the same factor to yield a constant  $\omega T$ .

From equation (2.8) it is recognized that  $|H(\omega T)| \leq 1$ . The maximum value occurs for the center frequency  $\omega_c$ , where  $\omega_c T = \pi/2$  and  $|H(\omega T)| = 1$ . To display all the fil-

ters on the same (normalized) frequency axis we assume that the sampling period T is fixed and then we multiply  $\omega$ T by  $N=2^k$  (k=0,1,...9), or successive powers of 2 to obtain the response of the lower frequency filters. For example, with k=1 (N=2) the center frequency of the filter occurs for  $\omega_c NT = \pi/2$  or  $\omega_c T = \pi/4$ , which corresponds to a denormalized frequency

$$\omega_{\rm c} = 2\pi f_{\rm c} = \frac{\pi}{4T} = 2\pi \frac{(64 \times 10^3)}{8}$$

or  $f_c=8$  KHz. Similarly, with k=2 (N=4)  $\omega_c T=\pi/8$  and the center frequency is  $f_c=4$  KHz, and so on. Finally, with k=9 (N=512) the center frequency is  $f_c=31.25$  Hz. When this N factor is included, equation (2.8) takes now the general form

$$|H(\omega T)| = \frac{\sin \omega NT}{\sqrt{4Q \cos^2 \omega NT + \sin^2 \omega NT}}$$

(2.9)

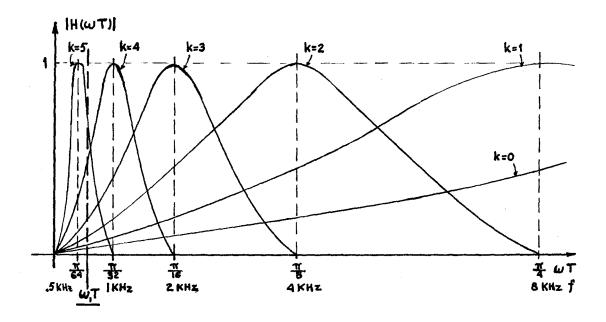

A few of the filters generated by varying the value of N in equation (2.9) are sketched in Figure 2.3 in a (linear) normalized frequency axis. The filters are numbered from right to left with k (0,1,2...) since the basic filter corresponds to the 16 KHz frequency. It will be noted that at any normalized frequency below  $\frac{\pi}{2}$ , the total output is contributed by the response of all the filters to the right and the one to the left of the frequency considered. Therefore, the total response at a frequency  $\omega_1$ T between the kth and the (k+1)th filter is given by (see Figure 2.3)

Figure 2.3 Response of the first 6 BPF's.

Figure 2.4 Response of all the BPF's in log scales.

$$|H(\omega_{1}T)| = \sum_{n=0}^{k+1} \frac{\sin 2^{n} \omega_{1}T}{\sqrt{4Q^{2}\cos^{2} 2^{n} \omega_{1}T + \sin^{2} 2^{n} \omega_{1}T}}$$

(2.10)

For low Q the response tends to have a sinusoidal shape and for practical purposes only the contribution of 4 or 5 filters to the right and one to the left of the given frequency need be considered.

Now we must determine the value of Q that will make the overall response as flat as possible. Due to the continuity of the responses we can do this numerically by trying different values of Q and calculating the response at several frequencies between the kth and the (k+1)th filter. We concluded that with a value of Q = 1 the response between two consecutive filters based in the contribution of 5 filters to the right and one to the left is within  $\pm 0.25$  dB, a quite acceptable result that is applicable to any pair of filters except the first four. Table 2.1 below shows the resultant outure for 10 intermediate frequencies normalized to the frequency of the (k+1)th filter, that is, varying between 1 and 2. It can be seen that the average output is about 1.823 and that the maximum and minimum deviations are within the range of  $\pm 0.25$  dB.

For frequencies of  $\pi/2$  (16 KHz) or larger only the first filter response contributes to the output. To compensate for the lower resultant output, the magnitude of this filter is multiplied by 1.823 to bring it up to the level of the other filters. In so doing, the total response at the

TABLE 2.1

| Normal- | Total output between the k and k+l filters* |         |         |         |         |  |  |

|---------|---------------------------------------------|---------|---------|---------|---------|--|--|

| ized    | k = 5                                       | k = 4   | k = 3   | k = 2   | k = 1   |  |  |

| Freq.   | N = 32                                      | N = 16  | N = 8   | N = 4   | N = 2   |  |  |

| 1.0     | 1.84294                                     | 1.83865 | 1.83044 | 1.81692 | 1.81527 |  |  |

| 1.1     | 1.89557                                     | 1.89087 | 1.88194 | 1.86800 | 1.87432 |  |  |

| 1.2     | 1.88429                                     | 1.87918 | 1.86957 | 1.85548 | 1.87199 |  |  |

| 1.3     | 1.85386                                     | 1.84834 | 1.83809 | 1.82415 | 1.85289 |  |  |

| 1.4     | 1.83160                                     | 1.82568 | 1.81483 | 1.80138 | 1.84375 |  |  |

| 1.5     | 1.82528                                     | 1.81896 | 1.80754 | 1.79495 | 1.85106 |  |  |

| 1.6     | 1.83237                                     | 1.82566 | 1.81372 | 1.80239 | 1.87003 |  |  |

| 1.7     | 1.84600                                     | 1.83890 | 1.82649 | 1.81675 | 1.89025 |  |  |

| 1.8     | 1.85740                                     | 1.84993 | 1.83709 | 1.82962 | 1.89825 |  |  |

| 1.9     | 1.85750                                     | 1.84965 | 1.83645 | 1.83162 | 1.87977 |  |  |

| 2.0     | 1.83865                                     | 1.83044 | 1.81692 | 1.81527 | 1.82300 |  |  |

<sup>\*</sup> The magnitude of the 16K BPF (N=2) is multiplied by 1.823

frequencies below  $\pi/2$ , where less number of filters are contributing to the output, is leveled with the response at all the other frequencies. The net effect is a uniform output accross the bands, as shown in Table 2.1.

Figure 2.4 shows the frequency response of all the filters plotted in a log frequency scale and with the output in dB's. The desired overall average gain is 1, but due to the

overlapping of the filters, it results about 1.823. Therefore, in the final implementation of the filters the gain coefficients of all of them, except the 16 KHz, are divided by 1.823.

With Q = 1, the final transfer function of our digital filter becomes

$$H(z) = \frac{1}{3} \frac{1 - z^{-2}}{1 + \frac{1}{3} z^{-2}}$$

(2.11)

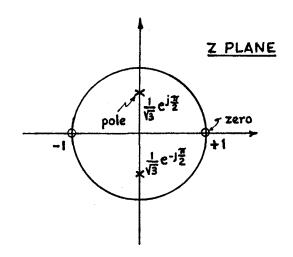

which has poles at  $z_1=(1/\sqrt{3})\mathrm{e}^{\mathrm{j}}\,\pi/2$  and  $z_2=(1/\sqrt{3})\mathrm{e}^{-\mathrm{j}}\,\pi/2$ , and zeros at  $z_3=1$  and  $z_4=-1$ , and it is therefore stable (see Figure 2.5).

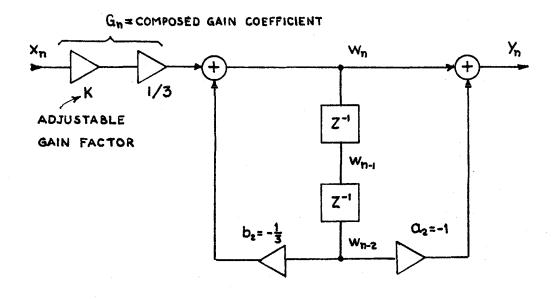

The final form of the filter is shown in Figure 2.6. The adjustable gain factors, which can be controlled from the front panel are integrated with the 1/3 factor of equation (2.11) to form the gain coefficient  $G_n$ .

The difference equations for the nth sample are obtained by partitioning the transfer function as follows

$$H(z) = \frac{Y(z)}{X(z)} = \frac{Y(z)}{W(z)} = \frac{W(z)}{X(z)} = G_n \quad \frac{1 - z^{-2}}{1 + \frac{1}{3} z^{-2}}$$

$$\frac{W(z)}{X(z)} = G_n \frac{1}{1 + \frac{1}{3} z^{-2}} \qquad \frac{Y(z)}{W(z)} = 1 - z^{-2}$$

from where the difference equations are

$$w_n = G_n.x_n - \frac{1}{3}w_{n-2}$$

(2.12)

$$y_n = w_n - w_{n-2}$$

(2.13)

Figure 2.5 Poles and zeros of H(z) for BPF.

Figure 2.6 Implementation of BPF of eq. (2.12, 2.13)

The intermediate results  $w_{n-1}$  and  $w_{n-2}$  are indicated in Figure 2.6. This is the form of the difference equation that is implemented in the program for the processor AMI S2811.

### Gain coefficients

For the calculation of the gain coefficients  $G_n$  we observe that 10 dB is equivalent to a factor of  $\sqrt{10}$ . However, we must take into account the fact that the output at a given frequency is contributed by the response of a few filters, mostly by the first to the right, that is, the next higher in frequency. We must emphasize at this point that the purpose of the equalizer is to shape the frequency response rather than to give an accurate output at each frequency. In practice, several adjacent BPF controls are usually adjusted to shape the response, so that the result depends on the combined effect of all of them.

To be more specific, we observe from Figure 2.3 that a given filter, say the 2 KHz, does not contribute any output at the center frequency of the higher order filter (4 KHz). The 4 KHz BPF, on the other hand, contributes about 45% of its output to the response at 2 KHz. Therefore, the gain control of the 2 KHz BPF affects only partially the overall response.

One way to improve the effect of the gain controls is to multiply the output of the next higher order filter (4 KHz in our example) by the same gain factor used for the BPF being processed. If this factor is 1, as in the O dB

gain setting, nothing will change. If the gain factor is not 1, the corresponding boosting or attenuation will be reinforced making more effective the action of the gain control. This multiplication is implemented in the program (see Chapter 3).

In practice, when only one gain control is adjusted, the resultant change will be 1 to 2 dB from the nominal setting. When two or more adjacent controls are adjusted, instead, the gains will be very close to the nominal values. To illustrate this point if, for example, we use a setting of -6 dB, that is, a factor of 0.5 in only one filter the overall attenuation at the filter frequency will be

$$20 \log_{1.823}^{0.5 + (0.823).0.5} = -4.5 \text{ dB}$$

where 1.823 is the reference output, as we know, and the values within parenthesis are the contribution of the BPF to the right of the one considered. If the adjacent BPF is also set to -6 dB, then the attenuation at the filter frequency will be

20

$$\log \frac{0.5 + (0.45)0.5^2 + (0.2)0.5 + (0.173)}{1.823} = -6.2 \text{ dB}$$

where the values within parenthesis are again the contribution of the BPF to the right, that is, those of higher frequencies.

The gain coefficients are then given by

$$G_n = \frac{1}{3} \log^{-1} \frac{A}{20}$$

where A is the gain setting in dB's and the factor 1/3 is the coefficient of equation (2.11) which, as we said, was to be integrated with  $G_{\rm n}$ .

There is another fact that must be taken into consideration. The SPP AMI S2811 only accepts numbers in the range -1 to +1. But for the highest setting of +10 dB, the factor is  $\sqrt{10}$  which is larger than 1. If this factor is used, the output of the respective BPF will be larger than 1. To avoid this possibility, we divide all the coefficients by  $\sqrt{10}$  and to make up for the difference we give a gain of  $\sqrt{10}$  or +10 dB to the output analog lowpass filter. Now the gain coefficient becomes

$$G_n = \frac{1}{3\sqrt{10}} \log^{-1} \frac{A}{20}$$

For example, with A=+10 dB,  $G_n=1/3$ . These numbers have to be stored in an 8-bit wide ROM in 2's complement form. We find that the 2's complement representation giving the minimum error (less than  $\frac{1}{2}LSB$ ) is 00101011 equivalent to decimal 0.3359. All the other coefficients are calculated in like manner and their values are included in Table 4.2 of Chapter 4 (page 87) along with the ROM addresses where they are stored.

As we said before, the 16 KHz BPF gain must be 1.823 times higher than the others to obtain a uniform response. This is implemented in the programming of the SPP by multiplying the gain of all the other filters by 1/1.823, while keeping the gain of the 16 KHz BPF at 1.

### 2. DIGITAL LOWPASS FILTERS

Every digital bandpass filter, except the one for the 16 KHz band, is preceded by a digital lowpass filter that limits the bandwidth of the sampled signal to below the folding frequency. For example, the 8 KHz BPF that receives the audio signal sampled at 32 KHz is preceded by a LPF with a cut-off frequency of 12 KHz and sufficient attenuation at the folding frequency of 16 KHz. The 4 KHz BPF has a 6 KHz LPF infront of it, and so forth. The 16 KHz BPF, on the other hand, receives the input signal sampled at 64 KHz and band limited to 21 KHz by an analog LPF (antialiasing filter) placed at the input of the equalizer, before the analog to digital conversion.

For the design of the digital lowpass filters we will use again the bilinear transformation, following this time the conventional method of design. The design is carried out for the first LPF with a cut-off frequency of 12 KHz and all the others are obtained by successively halving the sampling frequency, as we did with the bandpass filters (see Figure 2.1).

The specifications we set for our basic digital LPF are as follows:

Cut-off frequency, 12 KHz

Edge of stop band, 16 KHz

Attenuation in the stop band, > 30 dB

Ripple in the passband, < 0.5 dB

First, we normalize the digital frequencies to the sampling

frequency  $f_s = 64$  KHz. Then

Digital cut-off freq.

$$\omega_{c}T = \frac{2\pi (12 \times 10^{3})}{(64 \times 10^{3})} = \frac{3}{8}\pi$$

Edge of stop band

$$\omega_s^T = \frac{2\pi (16 \times 10^3)}{(64 \times 10^3)} = \frac{\pi}{2}$$

By applying the bilinear transformation of equation (2.3) we obtain the corresponding prewarped analog frequencies

$$\Omega_c = C \tan \frac{3\pi}{82}$$

(2.14)

$$\Omega_{s} = C \tan \frac{\pi}{4}$$

(2.15)

The resultant (prewarped) analog transition ratio is

$$r = \frac{\Omega_s}{\Omega_c} = \frac{\tan \frac{\pi}{4}}{\tan \frac{3\pi}{16}} = 1.4966$$

Hence, we must find an analog filter with a transition ratio of 1.4966, an attenuation in the stop band of more than 30 dB and a maximum ripple in the passband of 0.5 dB. From a handbook of filter design tables (Reference 8, p.66) we find that our specifications are met by a fourth order elliptic filter with a transition ratio of 1.4945, stopband attenuation of 33.5 dB and passband ripple of 0.28 dB. This filter has the standard factored form

$$H(s) = K \frac{s^2 + A_0}{s^2 + B_1 s + B_0} \cdot \frac{s^2 + C_0}{s^2 + D_1 s + D_0}$$

(2.16)

where the values of the coefficients for the normalized  $(\Omega_c = 1 \text{ rad/sec})$ transfer function are

$$K = 0.02124958$$

$C_0 = 11.98287105$   $A_0 = 2.51603207$   $D_0 = 0.58946535$   $D_1 = 1.08608904$   $D_1 = 0.28990329$

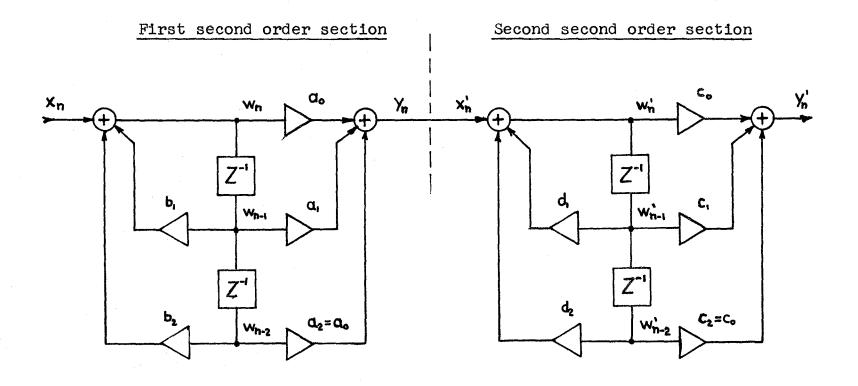

We see that this transfer function represents two cascaded second order filters. The corresponding digital filter has the general form

$$H(z) = K \frac{a_0 + a_1 z^{-1} + a_2 z^{-2}}{1 + b_1 z^{-1} + b_2 z^{-2}} \cdot \frac{c_0 + c_1 z^{-1} + c_2 z^{-2}}{1 + d_1 z^{-1} + d_2 z^{-2}} (2.17)$$

To apply the bilinear transformation from  $\underline{s}$  to  $\underline{z}$  of equation (2.1) we need to select the coefficient C. We do this by choosing to match the normalized digital cut-off frequency  $\omega_c T = (3/8) \pi$  to the normalized analog cut-off frequency  $\Omega_c = 1$  rad/sec. Then

$$\Omega_c = 1 \text{ rad/sec} = C \tan \frac{\omega_c T}{2} = C \tan \frac{3 \pi}{16}$$

Using this value of C, we can insert in equation (2.16) the expression for  $\underline{s}$  in terms of  $\underline{z}$  of equation (2.1), that

is, the bilinear transformation, to obtain the coefficients for H(z) in (2.17). This is facilitated by using the following relations taken from Reference 4, p. 174.

For the first second order section

$$A = B_0 + B_1 C + B_2 C^2$$

$$a_0 = (A_0 + A_1 C + A_2 C^2)/A$$

$$a_1 = (2A_0 - 2A_2 C^2)/A$$

$$a_2 = (A_0 - A_1 C + A_2 C^2)/A$$

$$b_1 = (2B_0 - 2B_2 C^2)/A$$

$$b_2 = (B_0 - B_1 C + B_2 C^2)/A$$

In our case  $A_1=0$  and  $A_2=B_2=1$ . Equivalent relations can be applied to the 2nd second order section. When th ulations are carried out and the gain coefficient K is integrated with the  $z^{-1}$  coefficients, the following transfer function results

$$H(z) = \frac{1 + a_1 z^{-1} + z^{-2}}{1 + b_1 z^{-1} + b_2 z^{-2}} \cdot \frac{c_0 + c_1 z^{-1} + c_0 z^{-2}}{1 + d_1 z^{-1} + d_2 z^{-2}}$$

(2.18)

where the coefficients have the following values:

$$a_0 = a_2 = 1$$

$c_0 = c_2 = 0.084994$

$a_1 = 0.116153$   $c_1 = 0.116448$

$b_1 = -0.588662$   $d_1 = -0.740947$

$b_2 = 0.771418$   $d_2 = 0.270239$

Figure 2.7 shows the diagramatic representation of the two second order sections. The intermediate values as well

Figure 2.7 Implementation of the 4th order LPF of eq. (2.19, 2.20)

as the input and output are primed for the second section.

From equation (2.18) the poles of the first section are found to be  $z_{1,2}=0.88/\pm70.4^{\circ}$ , and those of the second section  $z_{3,4}=0.52/\pm44.5^{\circ}$ . Since both pair of poles are inside the unit circle the filter is stable.

The difference equations for the nth. sample, derived from (2.18) by the same partitioning of the transfer function used in the BPF are

First section

$$w_{n} = x_{n} - b_{1}w_{n-1} - b_{2}w_{n-2}$$

$$y_{n} = w_{n} + a_{1}w_{n-1} + w_{n-2}$$

(2.19)

Second section

$$w_{n}^{\prime} = x_{n}^{\prime} - d_{1}w_{n-1}^{\prime} - d_{2}w_{n-2}^{\prime}$$

$$y_{n}^{\prime} = c_{0}w_{n}^{\prime} + c_{1}w_{n-1}^{\prime} + c_{0}w_{n-2}^{\prime}$$

(2.20)

These are the forms of the equations to be implemented as two cascaded second order sections in the programming of the SPP processor S2811. All the coefficients are between -1 and +1 and therefore no scaling is required.

# 3. ANALOG LOWPASS FILTERS

For the analog input (antialiasing) and output (smoothing) lowpass filters our specifications can be set as follows. In order to have a reasonable roll-off we will choose a cut-off frequency of about 20 KHz and an attenuation of about 30 dB at the folding frequency of 32 KHz. The rationale for these choices is that our input signal is bandlimited below 20 KHz first, because the spectral content of the musical material has inherently very little energy beyond 15 KHz and second, because the transmission media, FM broadcasting, records and tapes have bandwidths no wider than 20 KHz at best. For these reasons, the signal energy at 32 KHz is practically nil and 30 dB of attenuation at that frequency and beyond is more than sufficient to prevent aliasing.

For the output lowpass filter the same considerations are valid and besides the bandwidth of the output signal is limited to well below 32 KHz due to the response of the bilinear transformed bandpass filters. We therefore use the same filter design for the analog input and output lowpass filters. To complete our specifications we define a maximum ripple of 0.1 dB in the passband.

The transition width, normalized to the cut-off frequency is TW = (32 - 20)/20 = 0.6. From a Handbook of Active Filters (Reference 9) we find that an elliptic, 4-pole low-pass filter with 0.1 dB ripple and 30 dB attenuation in the stopband has a transition width of 0.53. Then, we can use

a cut-off frequency of 32 KHz/1.53 = 21 KHz. From the same handbook we obtain the transfer function of the filter

$$H(s) = K_1(c_1/a_1) \frac{s^2 + a_1 \omega_c}{s^2 + b_1 \omega_c s + c_1 \omega_c^2} K_2(c_2/a_2) \frac{s^2 + a_2 \omega_c}{s^2 + b_2 \omega_c s + c_2 \omega_c^2}$$

where  $K_1$  and  $K_2$  are the gains of the second order sections and the coefficients have the following values:

| $a_1 = 2.644233$         | $a_2 = 12.746572$         |

|--------------------------|---------------------------|

| b <sub>1</sub> =1.392323 | b <sub>2</sub> = 0.355395 |

| $c_1 = 0.854559$         | c <sub>2</sub> =1.261686  |

The cut-off radian frequency is  $\omega_c = 2\pi(21 \times 10^3)$ . Gains are  $K_1 = K_2 = 1$  for the input filter and  $10^{\frac{1}{4}}$  for the output filter.

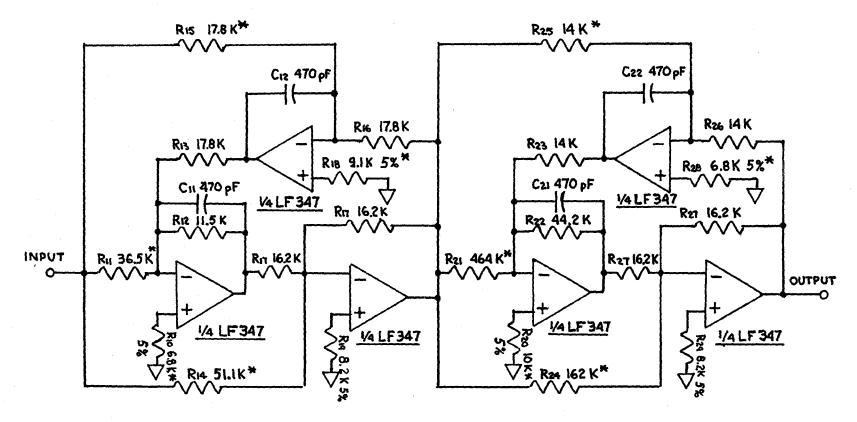

For easy of tuning we choose a biquad topology for each of the second order sections. Figure 2.8 is the schematic of the complete filter whose component values are calculated as follows, using the procedure of Reference 9, p. 65.

$K_1 = K_2 = 1$  for the input filter.  $K_1 = K_2 = 10^{\frac{1}{4}}$  for the output filter. All the values are the same for the input and output filters, except  $R_{11}$ ,  $R_{14}$  and  $R_{15}$ . All values are in ohms. The closest standard 1% values are indicated.

# A) First second order section

Value of  ${\rm C_{11}} = {\rm C_{12}}$  selected as 470 pF Using the values of  $\omega_{\rm c}$  and coefficients indicated above.

$$R_{11} = \frac{a_1}{\text{K.b}_{1.c}_{1.\omega_{c}.c}_{11}} = 35.8\text{K (use 36.5K) input}$$

20.1K (use 20.5K) output

$$R_{12} = \frac{1}{b_1 \cdot \omega_c \cdot c_{11}} = 11.6 \text{K (use 11.5K)}$$

$$R_{13} = \frac{1}{\sqrt{c_1} \cdot \omega_c \cdot c_{11}} = 17.4 \text{K (use 17.8K)}$$

$$R_{17} = \frac{1}{\omega_c \cdot c_{11}} = 16.1K \text{ (use 16.2K)}$$

$$R_{14} = \frac{a_1 \cdot R_{17}}{K \cdot c_1} = 50.1K \text{ (use 51.1K)}$$

input 28.2K (use 28.7K) output

$$R_{15} = \frac{1}{K. \sqrt{c_1}.\omega_c.c_{12}} = \frac{R_{13}}{K} = 17.8K$$

input 10K output

$$R_{16} = \frac{C_{11}}{C_{12}} R_{13} = R_{13} = 17.8 K$$

Resistors  $R_{10}$ ,  $R_{18}$  and  $R_{19}$  are calculated for lowest DC offset as the approximate parallel value of the input and feedback resistors, resulting

$$R_{19} = 8.1K$$

(use 8.2K, 5%)

## B) Second second order section

Same values of K. The component values for the second section are calculated as the first, using the appropriate coefficients. The results are:

$$C_{21} = C_{22} = 470 \text{ pF}$$

$$R_{21} = 458K$$

(use 464K) input 257K (use 261K) output

$$R_{22} = 45.3K$$

(use 44.2K)

$$R_{23} = 14.3K$$

(use 14.0K)

$$R_{27} = 16.1K$$

(use 16.2K)

$$R_{24} = 163K$$

(use 162K) input 92K (use 90.9K) output

$$R_{25} = 14.0K$$

input  $7.87K$  output

$$R_{26} = R_{23} = 14.0K$$

$$R_{20} = 10.6K$$

(use 10K, 5%) input 10.4K (use 10K, 5%) output

$$R_{28} = .7K$$

(use 6.8K, 5%) input 5K (use 5.1K, 5%) output

$$R_{29} = 8.1K$$

(use 8.2K,5%)

### NOTES

1. ALL RESISTOR VALUES IN OHMS, 1% UNLESS OTHERWISE INDICATED

2. RESISTOR VALUES ARE FOR INPUT LPF. VALUES MARKED \* ARE DIFFERENT IN THE OUTPUT LPF

Figure 2.8 Schematic of 4th order biquad elliptic LPF (LPF1, LPF2)

The requirements for the operational amplifiers are moderate. The input impedance should be large, at least 10 times the largest input resistor, or about 5 M $\Omega$ . The open loop gain at the cut-off frequency f $_{\rm C}$ , should be at least 50 times the gain of the filter, that is, 100 times or 40 dB in our case and its slew rate should be at least  $\frac{1}{2} {\rm V}_{\rm O} \omega_{\rm C}$  x 10<sup>-6</sup> V/usec, where V $_{\rm O}$  is the p-p output voltage, in our case 5V, giving a slew rate of 0.33 V/usec.

From the many types of op amps available we chose the National Semiconductor LF347, a quad JFET op amp with very high input impedance ( $10^{12}$  ohms), high slew rate of 13V/usec and open loop gain at 21 KHz in excess of 40 dB for  $\pm 15V$  supply. The distortion is very small, less than 0.02%, a good feature for our application. Since we need 2 filters or 12 op amps, 3 DIP would be sufficient for our implementation.

## CHAPTER 3

#### SOFTWARE DESIGN

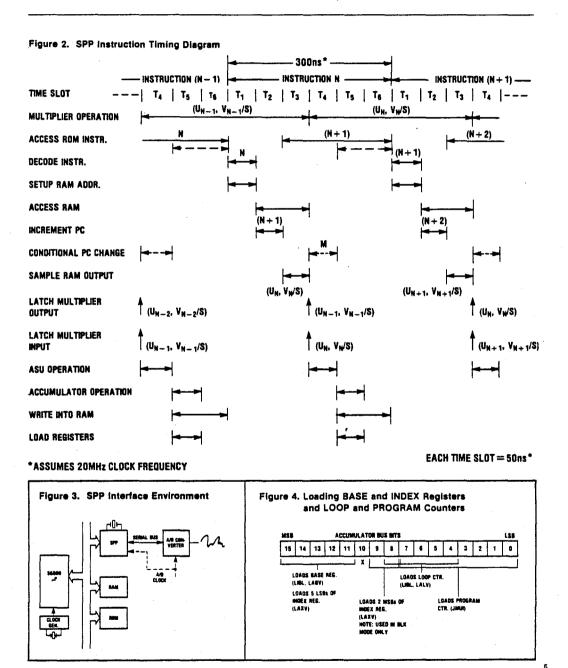

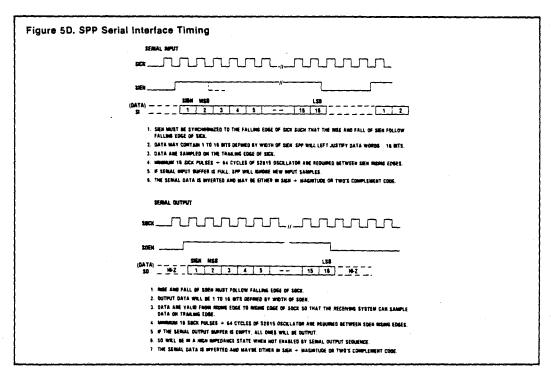

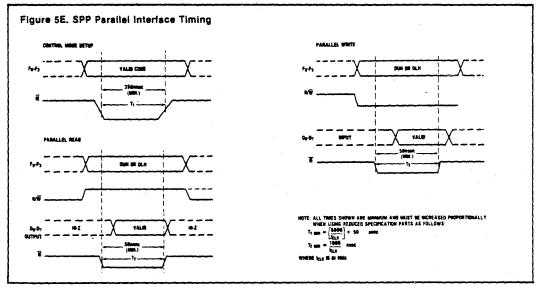

## 1. ARCHITECTURE AND PROGRAM FEATURES OF THE AMI S2811

The architecture and instruction set of the AMI S2811 SPP (Signal Processing Peripheral) is specially suited for the efficient processing of digital filters at high speed. At the clock frequency of 20 MHz, each instruction takes 300 nsec and due to the pipelined structure, only 5 instructions or 1.5 usec are required to process a secondorder recursive digital filter. In addition, two buffered serial ports clocked independently from the main processor, permit the input and output of data simultaneously with the program run. There is also an 8-bit bus to allow the input and output of data in parallel form. In all cases, the input data is held in the Input Register (IR) and the output data is placed in the Output Register(OR).

From the S2811 specifications sheet, it can be seen that the memory for the data is organized in a matrix of 32 Bases or rows, with each base having 8 locations of 16 bits each called displacements and numbered from 0 to 7 as illustrated in Figure 3.2. One half of this memory, comprising the displacements 0 to 3 of all the bases is RAM and the other half with locations 4 to 7 is mask programmable ROM. There is

also an 8-byte scratch pad RAM an of course, an instruction ROM capable of holding 256 programming steps.

The main memory can be accessed from two ports, labeled U and V and what makes this arrangement useful is that the two ports can be addressed simultaneously in one instruction, as long as the respective operands are stored in the same base. Alternatively, the scratch pad (S) can substitute for the port V in any instruction.

The instruction set has two type of operations that can be specified simutaneously in a single program step, except for a few cases of incompatibility. The OPI type of instruction includes all the arithmetic operations such as APA (Add Product and Accumulator), that adds the contents of the accumulator to the product of two multiplicands placed at the input of the multiplier in the previous instruction. The OP2 type of instruction refer to operations of loading, such as TIRV (Transfer Input Register to V location in RAM) or LACO (Load Accumulator in the Output Register); branching as in JMIF (Jump if I.F. is not set) and some miscellaneous such as DECB and INCB (Decrement and Increment the Base respectively).

The instruction word format contains two fields for the operations OP1 and OP2 and a field for the operand address. There are four addressing modes. One is the UV or US type, where two operands of the same Base or one operand from the Base (U) and one from the Scratch pad (S) are accessed at the same time. The Base Register that points to the Base No.

has to be set previously by inserting the desired Base No. through the instruction LIBL (Load the Input Register to the Base Register and Loop Counter) or by incrementing or decrementing the current Base No.

Other mode of addressing is the Direct Addressing D(XX.X) where the first two digits indicate the Base and the third, the Displacement. Only one operand can be accessed with this mode. The third mode is the Direct Transfer DT where a branching to a given address is specified, as in a Jump instruction. The fourth mode is called Literal an it just includes an OPl operation and a data word in the instruction.

A four line bus F can be used to control with external hardware (typically a microprocessor) several different modes of operation, such as setting the Serial Input or the Serial Output, addressing the upper byte of a two bytes word etc. When the SPP is not used in conjunction with a microprocessor, as in our case, those modes can be set from the program with the OP2 intruction MODE.

One useful feature of the SPP S2811 is the VP register that stores the operand from the V port specified in one instruction and makes it available in the following instruction with the command TVPV (Transfer contents of the VP register to V location in RAM) or TVIB (the same but incrementing the Base at the same time). This feature implements in software the  $z^{-1}$  delays of the digital filters.

It should be noted that the specified U and V (or S)

memory locations are placed at the input of the Multiplier during the same instruction, but the product is available in the following instruction. This product can be added to or substracted from the contents of the accumulator.

Besides the parallel bus and the serial input and output ports, the S2811 has an active LOW  $\overline{\text{RST}}$  input that clears all the registers, including the Base (not the RAM) and starts the program execution at the first instruction; an Interrupt Request ( $\overline{\text{IRQ}}$ ) output that goes LOW upon the execution of the instruction JMIF, that is, jump if the Input Flag (IF) is not set, indicating that no input of data has taken place, and an Interface Enable ( $\overline{\text{IE}}$ ) input to enable the parallel bus. The  $\overline{\text{IRQ}}$  output can also be set with the instruction JMOF, i.e., jump if the Output Flag (OF) is set.

# 2. MEMORY MAPPING

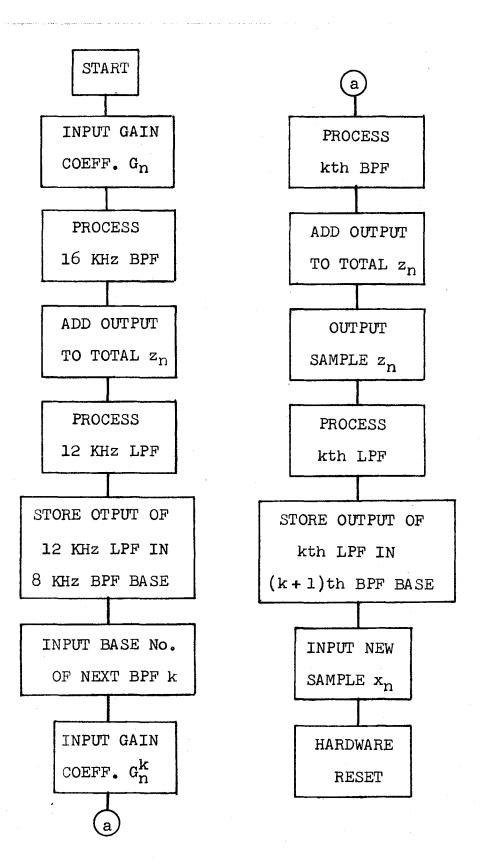

The flow chart of Figure 3.1 indicates the basic steps followed in the program. Two bandpass filters (BPF) and two lowpass filters (LPF) are processed in every program run, or equivalently, in every sampling period.

The memory mapping of Figure 3.2 shows how each BPF is stored in one base with the coefficients in ROM and the input sample and intermediate values in RAM. The LPF's, being of fourth order, require two bases for storage. A few points should be noted in the arrangement of the memory locations.

The highest frequency BPF (16 KHz) occupies the Base

No. O, followed by the highest frequency LPF (12 KHz) which

Figure 3.1 Flow chart of the signal processing

is taking Bases Nos. 1 and 2. The rest of the filters' data are stored in decreasing order of frequency; first one BPF followed by the LPF which processes the same sample according with the sequence depicted in Figure 2.1. The output of the LPF is placed in the next Base, to be used as the input "sample" for the next lower order BPF and LPF. This way, only the Base No. for the BPF needs to be inputted; the bases for the LPF are accessed by incrementing the Base No. with the instruction INCB.

Referring to the memory mapping of Figure 3.2 and the comments in the program, the notation  $x_n$  indicates the sample received from the Serial Input port which is always stored in location (00.0). The notation  $x_n^k$  denotes the sample after being filtered by the kth. LPF, that is, the output of that LPF. Other notations correspond to the nomenclature used in the respective difference equations of Chapter 2.

Due to limitations in the RAM space, the output of each BPF, such as  $y_n^{16K}$  is stored in the next lower Base and since it has to be saved for the next program run it becomes  $y_{n-1}^{16K}$ , as noted. The sum of all the BPF outputs,  $z_n$ , is stored in location 0 of the scratch pad memory (not shown in Figure 3.2). This sum, which constitutes the output of the audio equalizer after the D/A conversion, is updated after the processing of each BPF by adding to it the current output of the BPF and substracting the previous one. That is why those outputs must be saved in each program run.

| Base | e             | Displacement                        |                                          |                  |                   |                |                |                 |                 |

|------|---------------|-------------------------------------|------------------------------------------|------------------|-------------------|----------------|----------------|-----------------|-----------------|

| No   | Filter        | 0                                   | 1                                        | 2                | 3                 | 4              | 5              | 6               | 7               |

| 0    | 16 KHz<br>BPF | xn                                  | G <sub>n-1</sub>                         | wn-1             | wn-2              | <b>-1/</b> 3   | 1              |                 |                 |

| 1    | 12 KHz<br>LPF |                                     | у <mark>16К</mark><br>У <mark>n-1</mark> | w <sub>n-1</sub> | <b>w</b> n-2      | 1              | a <sub>l</sub> | -b <sub>l</sub> | -b <sub>2</sub> |

| 2    | 12 KHz<br>LPF |                                     |                                          | wh-1             | wi-2              | c <sub>o</sub> | c <sub>1</sub> | -d <sub>1</sub> | -d <sub>2</sub> |

| 3    | 8 KHz<br>BPF  | <b>x</b> 12K                        | G <sub>n-1</sub>                         | w <sub>n-1</sub> | wn-2              | <b>-1/</b> 3   | 1              | K               |                 |

| 4    | 6 KHz<br>LPF  | G <sub>n-1</sub>                    | y <sub>n-1</sub>                         | w <sub>n-1</sub> | <b>w</b> n-2      | 1              | a <sub>l</sub> | -b <sub>1</sub> | -b <sub>2</sub> |

| 5    | 6 KHz<br>LPF  |                                     |                                          | wn-1             | w <sub>1</sub> -2 | co             | c <sub>1</sub> | -d <sub>1</sub> | -d2             |

| 6    | 4 KHz<br>BPF  | x <sub>n</sub> 6K                   | G <sub>n-1</sub>                         | w <sub>n-1</sub> | wn-2              | <b>-1/</b> 3   | 1              | K               |                 |

|      |               |                                     | نـر (-                                   |                  |                   |                |                |                 |                 |

|      |               |                                     | •                                        |                  | •                 |                |                |                 | 1               |

|      |               | ·                                   | -                                        |                  | $ ^{\prime}$      |                |                |                 |                 |

| 24   | 62.5Hz<br>BPF | <b>x</b> n <sup>94</sup>            | G <sub>n-1</sub>                         | wn-1             | w <sub>n-2</sub>  | -1/3           | 1              | K               |                 |

| 25   | 47 Hz<br>LPF  | G <sub>n-1</sub>                    | y62.5                                    | wn-1             | <sup>₩</sup> n-2  | 1              | a <sub>l</sub> | -b <sub>1</sub> | -p <sup>5</sup> |

| 26   | 47 Hz<br>LPF  |                                     | -                                        | w <b>n</b> -1    | <b>w</b> i-2      | сo             | c <sub>1</sub> | -d <sub>1</sub> | -d <sub>2</sub> |

| 27   | 31 Hz<br>BPF  | <b>x</b> <sub>n</sub> <sup>47</sup> | G <sub>n-1</sub>                         | wn-1             | w <sub>n-2</sub>  | -1/3           | 1              | K               | ·               |

NOTES:  $x_n^{12K}$  denotes the sample filtered by the 12K LPF; etc.  $y_{n-1}^{8K}$  and  $G_{n-1}^{8K}$  denotes the output and gain factor respectively for the 8K BPF; etc. K=1/1.823

Figure 3.2. Memory mapping of SPP processor

## 3. THE PROGRAM

The following pages list the program steps with some brief comments related to the software implementation of equations (2.12), (2.13), (2.19) and (2.20). The SPP processor instruction set allows a lot of flexibility in the development of the program steps required to process the digital filters.

This portion of the project was one of major difficulties since the program had to be written in the most efficient way to compress in a short period of time (15.6 usec) the processing of two 2nd order BPF and two 4th order LPF plus the accumulation of the BPF outputs and overhead I/O instructions. The ability of the SPP to execute in one instruction the multiplication of two operands and the accumulation of the product, while the serial input and output are operating independently, permitted to achieve the necessary processing speed.

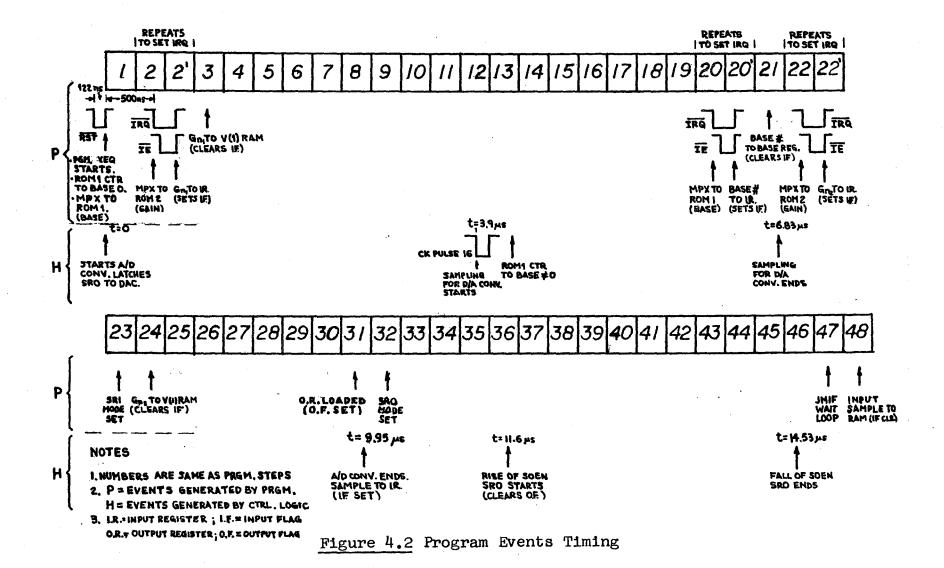

The flow chart of Figure 3.1 shows in block form the basic steps followed in the program. The interrelation between the program steps and the hardware operations is clarified in the Program Events timing of Figure 4.2, Chapter 4. In fact, both, the software and hardware operations had to be correlated so that the proper data is available at the proper time in the proper place. Figure 4.2 helps to understand the timing requirements of the relevant signals that are later implemented in the peripheral hardware, as explained in Chapter 4.

# PROGRAM

| STE | LABEL | <u>OPl</u> | OP2  | OPERAND   | COMMENTS                                               |

|-----|-------|------------|------|-----------|--------------------------------------------------------|

| 1   |       | DUH        | MODE | UV(3,4)   | 8-bit Mode set. Base = 0                               |

|     |       |            |      |           | $w_{n-2}$ , $a_2(-1/3) - MULT$ .                       |

| 2   | AGAIN | NOP        | JMIF | DT(AGAIN) | Waits for G <sub>n</sub> coeff. in-                    |

|     |       |            |      |           | put. Sets IRQ.                                         |

| 3   |       | A PZ       | TIRV | UV(0,1)   | w <sub>n-2</sub> ·a <sub>2</sub> —ACC.                 |

|     |       |            |      |           | $G_n \longrightarrow V(1).(Clears I.F.)$               |

|     |       |            |      |           | $x_n$ , $G_{n-1} \rightarrow MULT$ .                   |

| 4   |       | APA        | TACV | UV(-,2)   | $w_n = x_n \cdot G_{n-1} + a_2 \cdot w_{n-2} + ACC$    |

|     |       |            |      |           | $ACC(w_n) \longrightarrow V(2)$ .                      |

|     |       |            |      |           | $w_{n-1} - VP$ .                                       |

| 5   |       | SVA        | TVIB | UV(-,3)   | $w_{n-2} - w_n = -y_n \rightarrow ACC.$                |

|     |       |            |      |           | $w_{n-1} \rightarrow V(3)$ . Base incr.                |

| 6   |       | NEG        | TACV | UV(4,1)   | $-y_n \rightarrow y_n$ ; $y_n \rightarrow V(1)$ Base=1 |

|     |       |            |      |           | 1, $y_{n-1} \rightarrow MULT$ .                        |

| 7   |       | SPA        | DECB |           | $1.y_{n-1} - y_n \rightarrow ACC.$                     |

|     |       |            |      |           | Base decremented.                                      |

| 8 - |       | SVA        | TACV | US(-,0)   | $z_{n=z_{n-1}}-(y_{n-1}-y_n) \rightarrow ACC.$         |

|     |       |            |      | •         | $z_n \longrightarrow S(0)$ (Update total)              |

|     | •     |            |      |           | Base= 0                                                |

| STEP LABEL | <u>OP1</u> | <u>0P2</u> | OPERAND          | COMMENTS                                                                                                          |

|------------|------------|------------|------------------|-------------------------------------------------------------------------------------------------------------------|

| 9          | AVZ        | INCB       | UV(-,0)          | $x_n \rightarrow ACC$ . (From Base O)                                                                             |

|            |            |            |                  | Base incremented.                                                                                                 |

|            |            |            |                  | Starts LPF (12 KHz).                                                                                              |

| 10         | NOP        | NOOP       | w(6,2)           | $w_{n-1}$ ; $-b_1 \rightarrow MULT$ . Base = 1                                                                    |

| 11         | APA        | NOOP       | υν(7 <b>,</b> 3) | $x_n - b_1 \cdot w_{n-1} - ACC$ .                                                                                 |

|            |            |            |                  | $w_{n-2}$ ; $-b_2 \rightarrow MULT$ .                                                                             |

| 12         | A PA       | TACV       | υν(5,2)          | $\mathbf{w}_{n} = \mathbf{x}_{n} - \mathbf{b}_{1} \cdot \mathbf{w}_{n-1} - \mathbf{b}_{2} \cdot \mathbf{w}_{n-2}$ |

|            |            |            |                  | $w_n \rightarrow ACC. \rightarrow V(2)$ . Replaces                                                                |

|            |            |            |                  | $w_{n-1}$ . $w_{n-1} \rightarrow VP$ .                                                                            |

|            |            |            |                  | $w_{n-1}$ ; $a_1 \longrightarrow MULT$ .                                                                          |

| 13         | A PA       | TVIB       | UV(4,3)          | $w_n + a_1 \cdot w_{n-1} \rightarrow ACC$ .                                                                       |

|            |            |            |                  | $w_{n-1} \rightarrow V(3)$ Replaces $w_{n-2}$                                                                     |

|            |            |            |                  | 1; $w_{n-2} \rightarrow MULT$ .                                                                                   |

|            |            |            | ,                | Base incremented.                                                                                                 |

| 14         | A PA       | NOOP       | UV(6,2)          | $x_{n} = y_{n} = w_{n} + a_{1} \cdot w_{n-1} + w_{n-2}$                                                           |

|            |            |            |                  | $y_n \rightarrow ACC$ . Base = 2.                                                                                 |

|            |            |            |                  | $w_{n-1}$ ;-d <sub>1</sub> MULT.                                                                                  |

| 15         | A PA       | NOOP       | UV(7,3)          | $x_{n}^{\dagger} - d_{1} \cdot w_{n-1}^{\dagger} - ACC$ .                                                         |

|            |            |            |                  | $w_{n-2}^{\dagger}$ ;- $d_2$ -MULT.                                                                               |

| 16         | APA        | TACV       | w(5,2)           | $w_{n}^{\prime} = x_{n}^{\prime} - d_{1} \cdot w_{n-1}^{\prime} - d_{2} \cdot w_{n-2}^{\prime}$                   |

|            |            |            |                  | $w_n \rightarrow ACC \rightarrow V(2)$ . Replaces                                                                 |

|            |            |            |                  | $w_{n-1}^{\prime}$ . $w_{n-1}^{\prime}$ $\rightarrow$ $VP$                                                        |

| STEP | LABEL | <u>OP1</u> | <u>OP2</u> | OPERAND  | COMMENTS                                                                                                                |

|------|-------|------------|------------|----------|-------------------------------------------------------------------------------------------------------------------------|

|      |       |            |            |          | $w_{n-1}^{\prime}$ ; $c_1 \rightarrow MULT$ .                                                                           |

| 17   |       | APZ        | TVPV       | uv(4,3)  | $c_1.w_{n-1}$ —ACC.<br>$w_{n-1}$ —V(3) Replaces $w_{n-2}$<br>$w_{n-2}$ ; $c_0$ —MULT.                                   |

| 18   |       | APA        | INCB       | UV(4,2)  | $c_1.w_{n-1} + c_0.w_{n-2} \rightarrow ACC.$ $w_n'; c_0 \rightarrow MULT.$ Base incremented.                            |

| 19   |       | APA        | TACV       | UV(-,0)  | $y'_n = c_0 \cdot w'_n + c_1 \cdot w'_{n-1} + c_0 \cdot w'_{n-2}$<br>$y'_n \rightarrow ACC \rightarrow V(0)$ . Base = 3 |

| 20   | NEXT  | NOP        | JMIF       | DT(NEXT) | Waits for next Base No.                                                                                                 |

| 21   |       | NOP        | LIBL       |          | Base No. of next BPF to Base Reg. Clears I.F.                                                                           |

| 22   | SAME  | NOP        | JMIF       | DT(SAME) | Waits for $G_n^k$ coeff. input. Sets $\overline{IRQ}$ . Base=B                                                          |

| 23   |       | SRI        | MODE       | UV(3,4)  | Second BPF starts.  a <sub>2</sub> ; w <sub>n-2</sub> →MULT  Serial Input Mode set.                                     |

| 24   |       | APZ        | TIRV       | UV(0,1)  | $w_{n-2}.a_2 \rightarrow ACC.$ $G_n^k \rightarrow V(1).$ Clears I.F. $x_n^k; G_{n-1}^k \rightarrow MULT.$               |

| STEP LABEL | <u>OP1</u> | OP2  | OPERAND | COMMENTS                                                                  |

|------------|------------|------|---------|---------------------------------------------------------------------------|

| 25         | APA        | TACV | UV(-,2) | $w_n = x_n^k \cdot G_{n-1}^k - a_2 \cdot w_{n-2} \rightarrow ACC$         |

|            |            |      |         | $ACC(w_n) \rightarrow V(2); w_{n-1} \rightarrow VP$                       |

| 26         | SVA        | TVIB | UV(-,3) | $w_{n-2} - w_n = -y_n \longrightarrow ACC$                                |

|            |            |      |         | $W_{n-1} \rightarrow V(3)$ . Base incr.                                   |

| 27         | NEG        | TACV | UV(0,1) | $-y_n \rightarrow y_n \rightarrow V(1).Base = B+1$                        |

|            |            |      |         | $G_{n-1}^{k+1}$ ; $y_{n-1} \rightarrow MULT$ .                            |

| 28         | APZ        | NOOP | UV(0,1) | 11-1                                                                      |

|            |            |      |         | $G_{n-1}^{k+1}; y_n \rightarrow MULT.$                                    |

| 29         | SPA        | DECB |         | $y_n.g_{n-1}^{k+1} - y_{n-1}.g_{n-1}^{k+1} \rightarrow ACC$<br>Base decr. |

|            |            |      |         |                                                                           |

| 30         | AVA        | TACV | US(-,0) | $z_{n} = z_{n-1} + y_{n} G_{n-1}^{k+1} - y_{n-1} G_{n-1}^{k+1}$           |

|            |            |      |         | $z_n \longrightarrow ACC \longrightarrow S(0)$ . Base = B                 |

| 31         | NOP        | LACO | υν(1,6) | $z_n \rightarrow OR$ $G_n^k$ ; $K \rightarrow MULT$ .                     |

| 32         | APZ        | TACV | UV(-,1) | $G_n^k$ . $K \rightarrow ACC \rightarrow V(1)$                            |

| 33         | AVZ        | INCB | UV(-,1) | $x_n^k \rightarrow ACC$ , Base incr.                                      |

| 34         | SRO        | MODE | uv(6,2) | w <sub>n-1</sub> ,b <sub>1</sub> MULT.                                    |

|            |            |      |         | Base = B+1.SRO Mode set                                                   |

| 35         | APA        | NOOP | υν(7,3) | $x_n^k - b_1 \cdot w_{n-1} \longrightarrow ACC.$                          |

|            |            |      |         | $w_{n-2}$ ; $-b_2 \xrightarrow{n-1} MULT$ .                               |

|            |            |      |         |                                                                           |